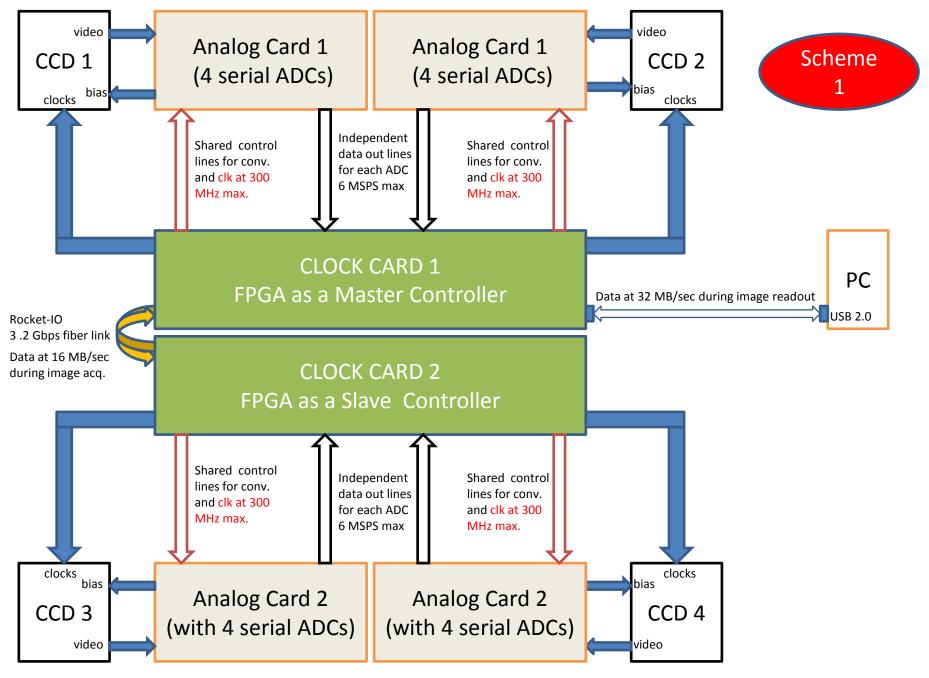

## Scheme 1

- One USB interface to handle 4 CCDs

- 4 host computers shall be required for ZTFC (16 CCDs)

- Each FPGA reads data from 8 ADCs and performs DCDS

- Maximum data throughput rate would be 32 MBytes / sec per interface

- Reading ADCs at 300 MHz clock is going to be a challenge (current code uses 100 MHz clock).

IFPAC data flow schemes for ZTFC, Mahesh Burse, IUCAA

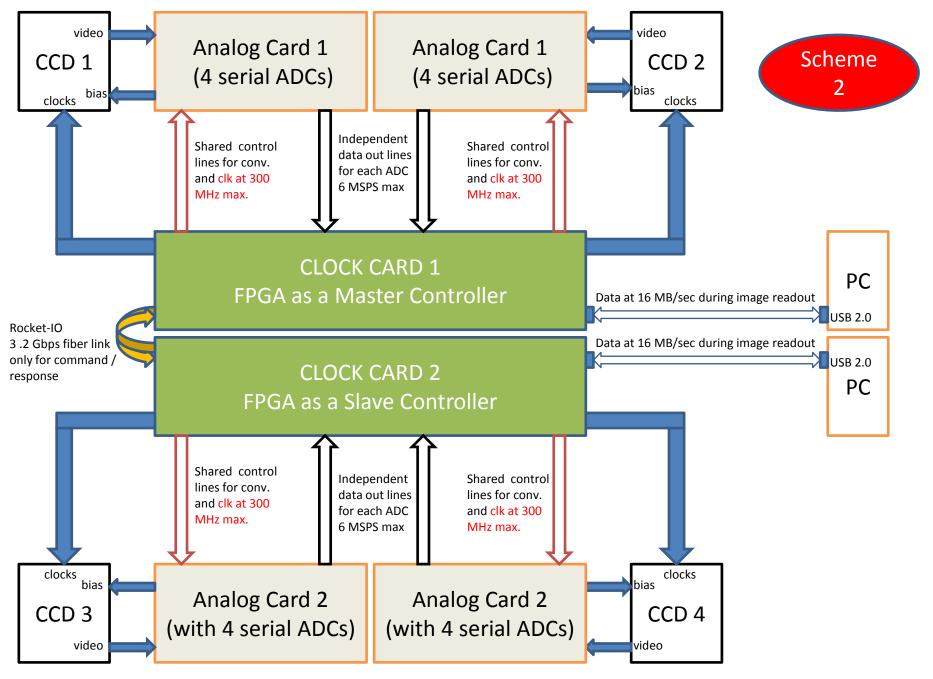

## Scheme 2

- One USB to handle all commands for 4 CCDs plus image data readout from 8 ADCs (2 CCDs)

- Other USB only for image data acquisition from 8 ADCs (2 CCDs)

- 8 host computers shall be required for ZTFC (16 CCDs)

- Each FPGA reads data from 8 ADCs and performs DCDS

- Maximum data throughput rate would be 16 MBytes/sec per interface

- Reading ADCs at 300 MHz clock is going to be a challenge (current code uses 100 MHz clock).

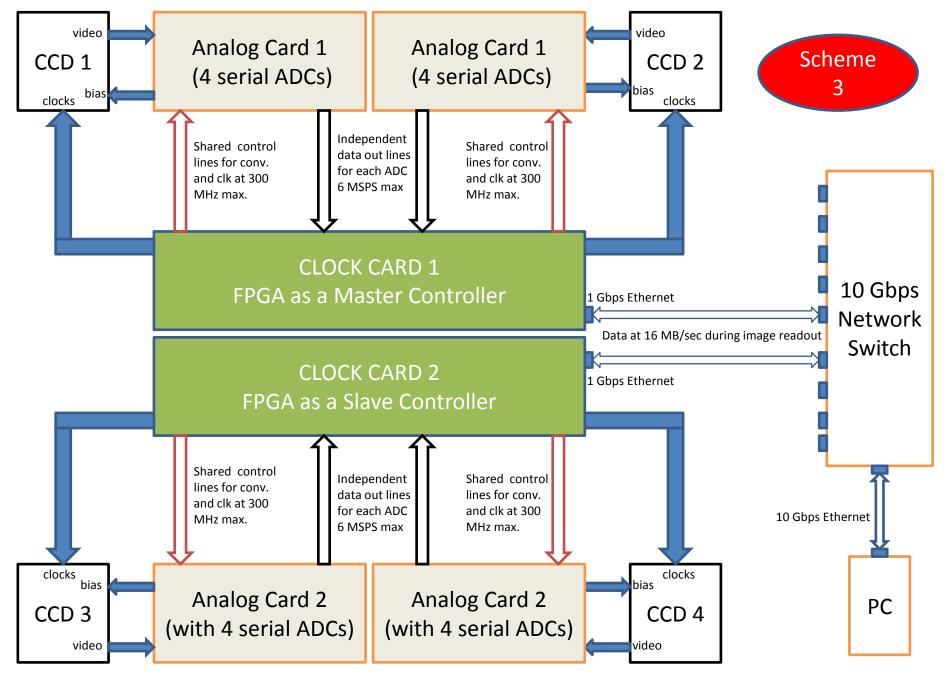

## Scheme 3

- 1 Gbps Ethernet link per clock card

- Each clock card to read 8 ADCs (2 CCDs) and perform DCDS

- 16 links would be required for ZTFC

- All links can be terminated into 10 Gbps network switch

- Reading ADCs at 300 MHz clock is going to be a challenge (current code uses 100 MHz clock).

- Present clock card can support only UDP, due to this data packets could be lost due to busy network or for other reasons

IFPAC data flow schemes for ZTFC, Mahesh Burse, IUCAA