## **KECK NEXT GENERATION WAVEFRONT CONTROLLER**

# Real Time Controller As Built Design Document

| Document :    | NGWFC_RTC_ASB_00              | J2.doc |

|---------------|-------------------------------|--------|

| Issue:        | 2                             |        |

| Date :        | March 28 <sup>th</sup> , 2011 |        |

| Prepared by : | MICROGATE                     |        |

|               | R.Biasi                       |        |

|               | D.Pescoller                   |        |

|               | M.Andrighettoni               |        |

| Checked by:   |                               |        |

|               |                               |        |

| Approved by:  |                               |        |

|               |                               |        |

| Released by:  |                               |        |

Doc. : NGWFC\_RTC\_ASB\_002.doc Issue : 2 – March 28<sup>th</sup> , 2011

Page : 2 of 211

## CHANGE RECORDS

| ISSUE | DATE       | Author    | Approved | QA/<br>QC | SECTION /<br>PARAG.<br>AFFECTED                                                                                                                            | REASON/INITIATION<br>DOCUMENTS/REMARKS |

|-------|------------|-----------|----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1     | 2007.09.02 | Microgate |          |           | All                                                                                                                                                        | First Issue                            |

| 2     | 2011.03.28 | Microgate |          |           | 1, 2, 4, 5, 6.1.1.7, 6.1.3, 6.3.2.3, 6.4.1, 6.4.2, 6.4.3, 7.1.1, 7.1.1.1, 7.1.1.2, 7.1.3.1, 7.1.6, 7.1.7.1, 7.1.7.2, 7.1.7.2.2, 7.1.8, 7.3.2, 7.4.1, 8.4.9 | Updated for NIR-TT PDR                 |

Doc. : NGWFC\_RTC\_ASB\_002.doc lssue : 2 – March 28<sup>th</sup> , 2011

Page: 3 of 211

## **TABLE OF CONTENTS**

| 1 | ACRON  | NYMS                                      | 12 |

|---|--------|-------------------------------------------|----|

| 2 | APPLIC | CABLE DOCUMENTS                           | 14 |

| 3 | REFERI | ENCE DOCUMENTS                            | 16 |

| 4 | INTRO  | DUCTION                                   | 17 |

| 5 | SYSTE  | M OVERVIEW                                | 18 |

| 6 | HARD\  | WARE DESIGN                               | 21 |

|   | 6.1 V  | VIF/WFP HARDWARE                          | 21 |

|   | 6.1.1  | Microgate Adaptive Optics crate (MGAOS)   | 21 |

|   | 6.1.2  | VME components                            | 66 |

|   | 6.1.3  | Power dissipation                         | 68 |

|   | 6.1.4  | Power supply system                       | 68 |

|   | 6.1.5  | Mechanical aspects and cooling            | 70 |

|   | 6.2 T  | RS HARDWARE                               | 70 |

|   | 6.2.1  | Storage Server                            | 70 |

|   | 6.2.2  | Disk array                                | 71 |

|   | 6.3 H  | W Interfaces                              | 72 |

|   | 6.3.1  | Internal HW interfaces                    | 73 |

|   | 6.3.2  | External HW interfaces                    | 75 |

|   | 6.4 R  | ELIABILITY                                | 79 |

|   | 6.4.1  | MGAOS system reliability prediction       | 79 |

|   | 6.4.2  | Complete VME crate reliability prediction | 81 |

|   | 6.4.3  | TRS system reliability                    | 81 |

|   | 6.4.4  | Spares                                    | 82 |

| 7 | SOFTW  | /ARE DESIGN                               | 83 |

|   | 7.1 N  | 1GAOS Software                            | 83 |

8

## NGWFC REAL TIME CONTROLLER As Built Data Package

Doc. : NGWFC\_RTC\_ASB\_002.doc Issue : 2 – March 28<sup>th</sup> , 2011

Page : 4 of 211

| 7.1.  | 1 MGAOS data flow                                        | 83  |

|-------|----------------------------------------------------------|-----|

| 7.1.2 | 2 MGOAS DSP codes description                            | 106 |

| 7.1.3 | 3 Centroids computation                                  | 123 |

| 7.1.4 | Residual Wavefront computation                           | 126 |

| 7.1.5 | 5 Control law servo computation                          | 127 |

| 7.1.6 | 6 HVC real-time control software                         | 127 |

| 7.1.7 | 7 Telemetry data                                         | 131 |

| 7.1.8 | 3 On-the-fly parameter swapping                          | 137 |

| 7.2   | MVME6100 SOFTWARE                                        | 137 |

| 7.2.2 | 1 System start-up                                        | 137 |

| 7.2.2 | 2 WIF/WCP interface                                      | 139 |

| 7.2.3 | System monitoring                                        | 148 |

| 7.2.4 | System configuration storage to TRS                      | 148 |

| 7.2.5 | 5 MVME6100 software structure                            | 149 |

| 7.3   | TRS                                                      | 153 |

| 7.3.2 | 2 Database layout                                        | 157 |

| 7.4   | SW Interfaces                                            | 162 |

| 7.4.2 | 1 Internal SW interfaces                                 | 162 |

| 7.4.2 | 2 External SW interfaces                                 | 162 |

| ANN   | IEX                                                      | 163 |

| 8.1   | MGP COMMANDS LIST                                        | 163 |

| 8.2   | POSTGRESQL                                               | 204 |

| 8.3   | FINAL COTS SELECTION                                     | 205 |

| 8.4   | MICROGATE BOARDS SCHEMATICS, LAYOUT AND BILL OF MATERIAL | 206 |

| 8.4.2 | 1 AdOpt BCU 4.0                                          | 206 |

| 8.4.2 | 2 AdOpt Ethernet PCI 1.1                                 | 207 |

Doc. : NGWFC\_RTC\_ASB\_002.doc Issue : 2 – March 28<sup>th</sup> , 2011

Page : 5 of 211

|     | 8.4.3  | AdOpt Fastlink 2.0         | . 207 |

|-----|--------|----------------------------|-------|

|     | 8.4.4  | AdOpt DSP Digital Only 3.1 | . 207 |

|     | 8.4.5  | AdOpt DSP HVC 3.2          | . 208 |

|     | 8.4.6  | AdOpt HVC 1.0              | . 209 |

|     | 8.4.7  | AdOpt AIA to PIO 2.0       | . 209 |

|     | 8.4.8  | AdOpt PIO to DM 1.0        | . 210 |

|     | 8.4.9  | AdOpt NIR-TT to BCU 1.0    | . 210 |

|     | 8.4.10 | AdOpt Reset Board 1.0      | . 210 |

|     | 8.4.11 | AdOpt Backplane 2.1        | . 211 |

| Q I | 5 C    | ODE REFERENCE              | 211   |

Doc.: NGWFC\_RTC\_ASB\_002.doc Issue: 2 – March 28<sup>th</sup>, 2011

Page : 6 of 211

# **LIST OF FIGURES**

| Figure 1 – NGWFC RTC global architecture                                                                                            | 19 |

|-------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2 – NGWFC RTC: VME and MGAOS crate mechanical layout                                                                         | 20 |

| Figure 3 – BCU board block scheme                                                                                                   | 24 |

| Figure 4 – High speed communication paths                                                                                           | 30 |

| Figure 5 – Diagnostic communication paths                                                                                           | 32 |

| Figure 6 – BCU board components placing, with evidence of the different functional zones                                            | 34 |

| Figure 7 – BCU board                                                                                                                | 35 |

| Figure 8 – DSP boards block scheme. The shaded parts refer only to the DSP board mounted on the HVC board                           |    |

| Figure 9 – DSP board components placing, with evidence of the different functional zones                                            | 41 |

| Figure 10 – DSP board V3.0. The board in this picture is completely mounted, including the analog parts used only on the HVC board. |    |

| Figure 11 - HVC driver board                                                                                                        | 43 |

| Figure 12 - HVC "mother" board                                                                                                      | 43 |

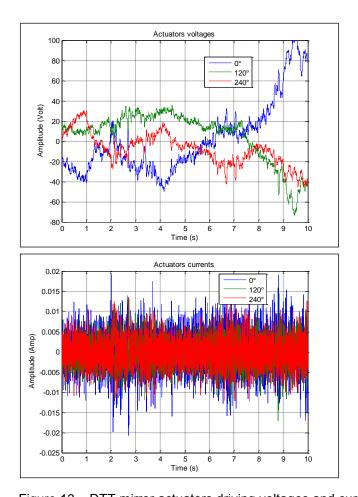

| Figure 13 – DTT mirror actuators driving voltages and currents for typical 'bad seeing' compensation                                | 46 |

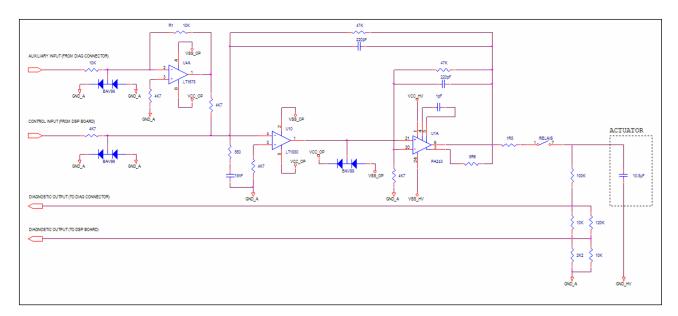

| Figure 14 – High voltage drive output stage                                                                                         | 48 |

| Figure 15 – HVC board mechanical layout                                                                                             | 50 |

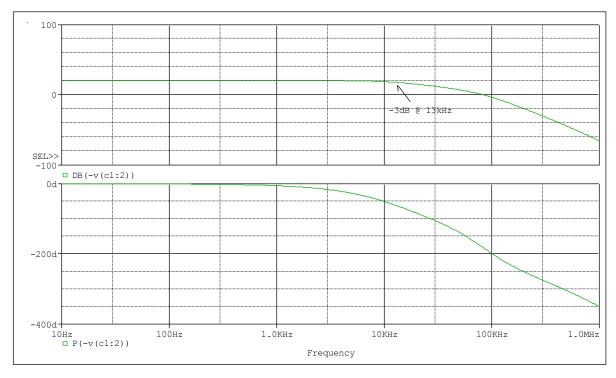

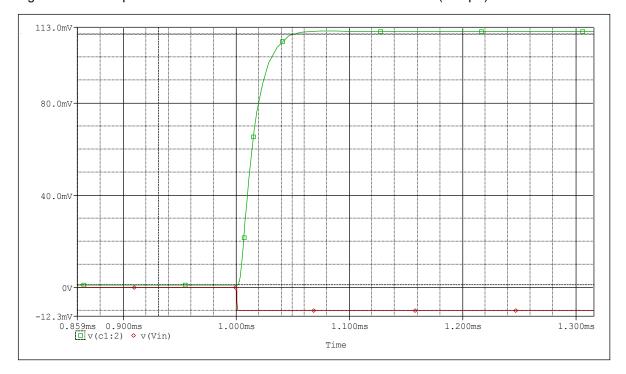

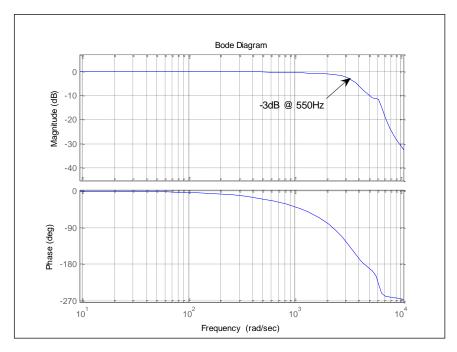

| Figure 16 – Bode plot of actuator drive electronics. DTT mirror actuator (10.8μF)                                                   | 51 |

| Figure 17 – Step response of actuator drive electronics. DTT mirror actuator (10.8μF)                                               | 51 |

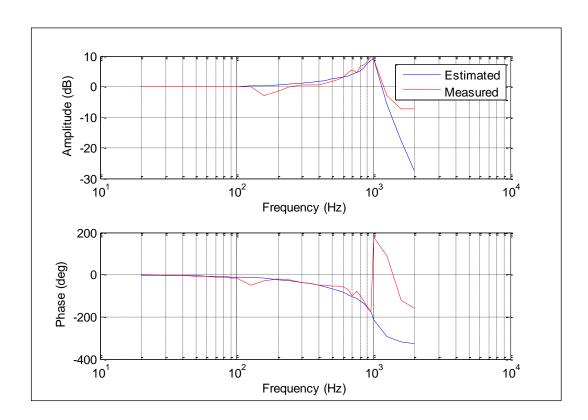

| Figure 18 – Estimated vs. actual mirror transfer function                                                                           | 52 |

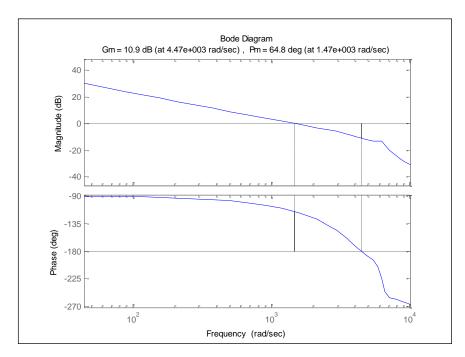

| Figure 19 – DTT control. Closed loop transfer function with gain and phase margins                                                  | 53 |

| Figure 20 – DTT control. Error transfer function with gain and phase margins                                                        | 53 |

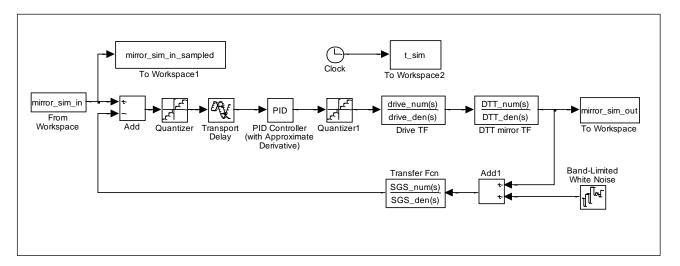

| Figure 21 – Simulation block diagram.                                                                                               | 54 |

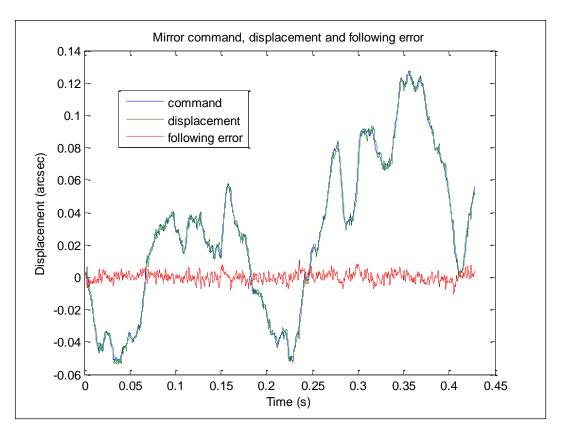

| Figure 22 – Simulation of a 'bad seeing' input to actuator at 0 deg.                                                                | 55 |

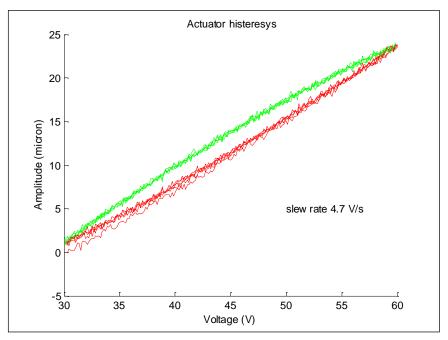

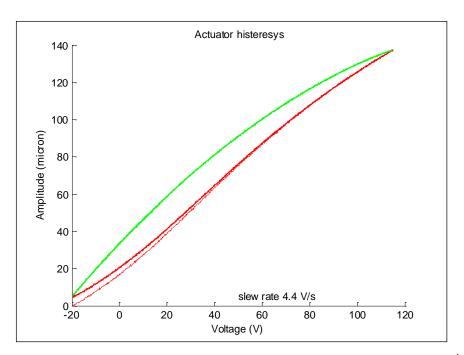

| Figure 23 – Actuator histeresys. Voltage span: 30/60V, slew rate 4.7Vs <sup>-1</sup>                                                | 57 |

Doc. : NGWFC\_RTC\_ASB\_002.doc lssue : 2 – March 28<sup>th</sup> , 2011

Page: 7 of 211

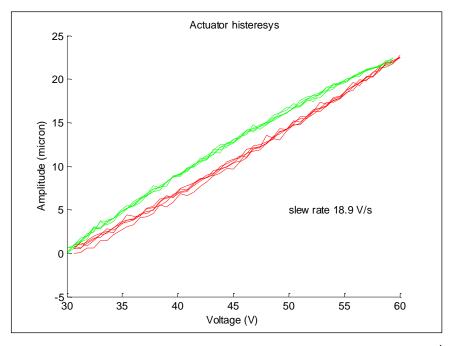

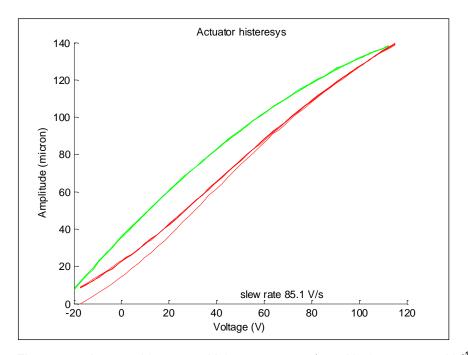

| Figure 24 – Actuator histeresys. Voltage span: 30/60V, slew rate 18.9Vs <sup>-1</sup>                     | 57  |

|-----------------------------------------------------------------------------------------------------------|-----|

| Figure 25 – Actuator histeresys. Voltage span: -20/+115V, slew rate 4.4Vs <sup>-1</sup>                   | 58  |

| Figure 26 – Actuator histeresys. Voltage span: -20/+115V, slew rate 85.1Vs <sup>-1</sup>                  | 58  |

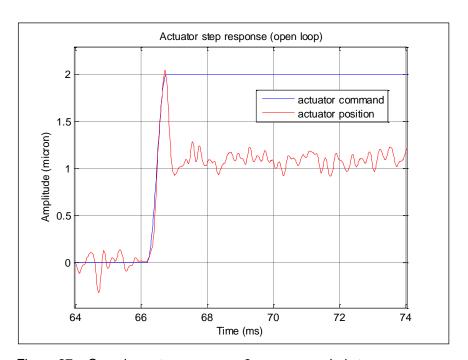

| Figure 27 – Open loop step response, 2μm commanded step                                                   | 59  |

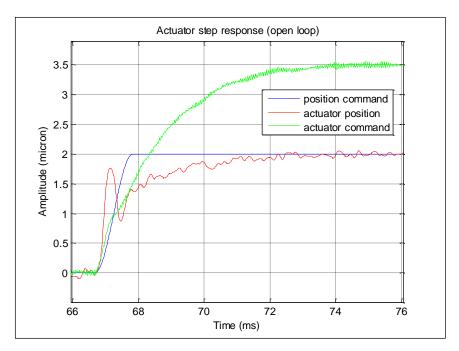

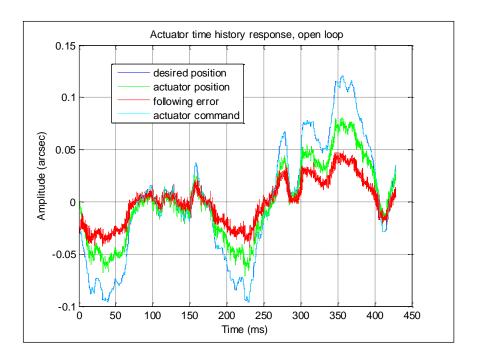

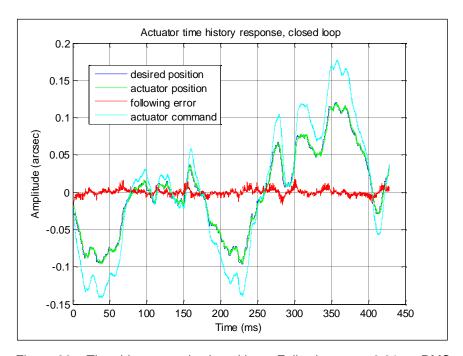

| Figure 28 – Closed loop step response, 2μm commanded step                                                 | 60  |

| Figure 29 – Time history test in open loop. Following error: 1.69µm RMS corresponding to 21.2 r<br>on-sky |     |

| Figure 30 – Time history test in closed loop. Following error: 0.31µm RMS corresponding to 3.86 on-sky    |     |

| Figure 31 – Step response auto-tuning                                                                     | 63  |

| Figure 32 – Oscillation detection                                                                         | 64  |

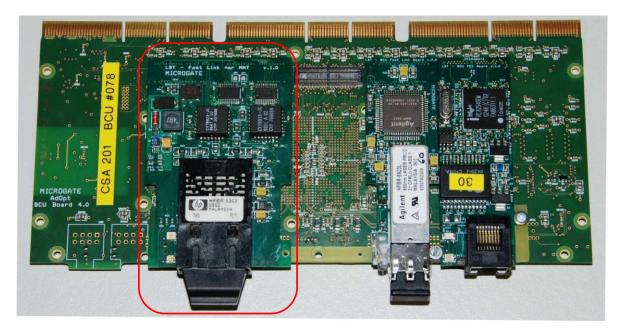

| Figure 33 - NIR-TT sensor to BCU interface board installed on Microgate BCU                               | 66  |

| Figure 34 - RTC main scheme                                                                               | 84  |

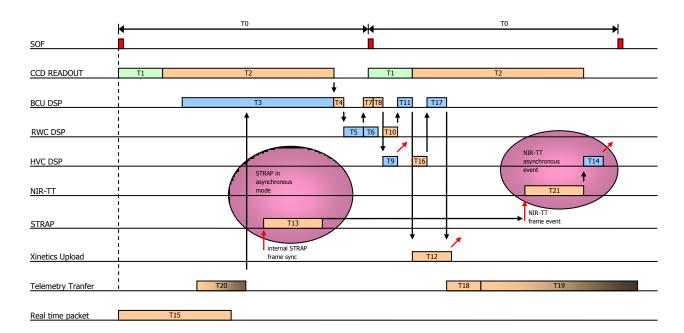

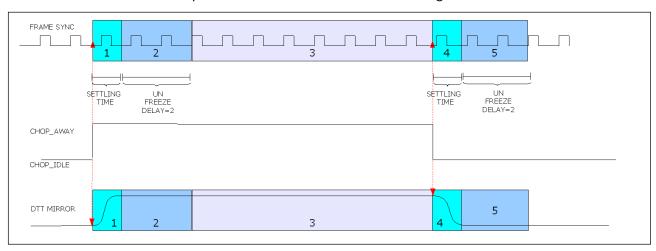

| Figure 35 - Real time sequence with asyncronous slave STRAP and master NIR-TT                             | 105 |

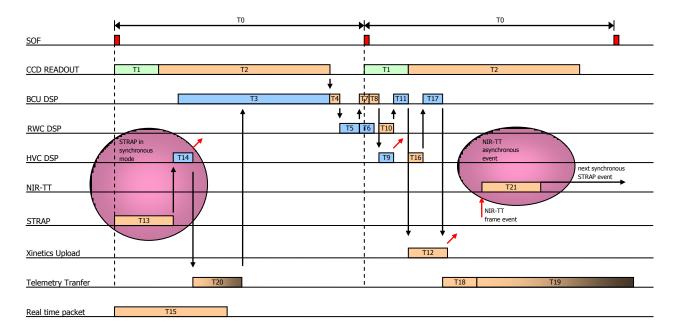

| Figure 36 - Real time sequence with syncronous and master STRAP and slave NIR-TT                          | 105 |

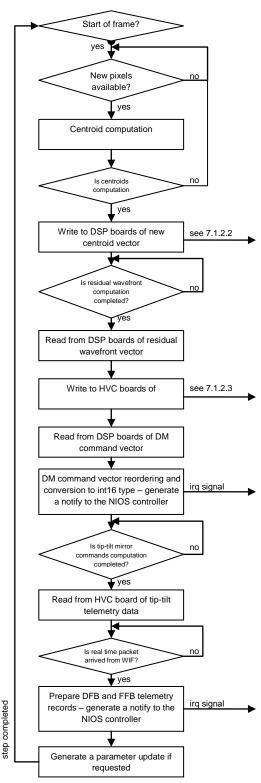

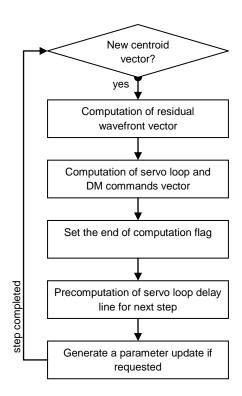

| Figure 37 - flow chart of DSP code of BCU board                                                           | 108 |

| Figure 38 - flow chart of DSP code of DSP boards                                                          | 109 |

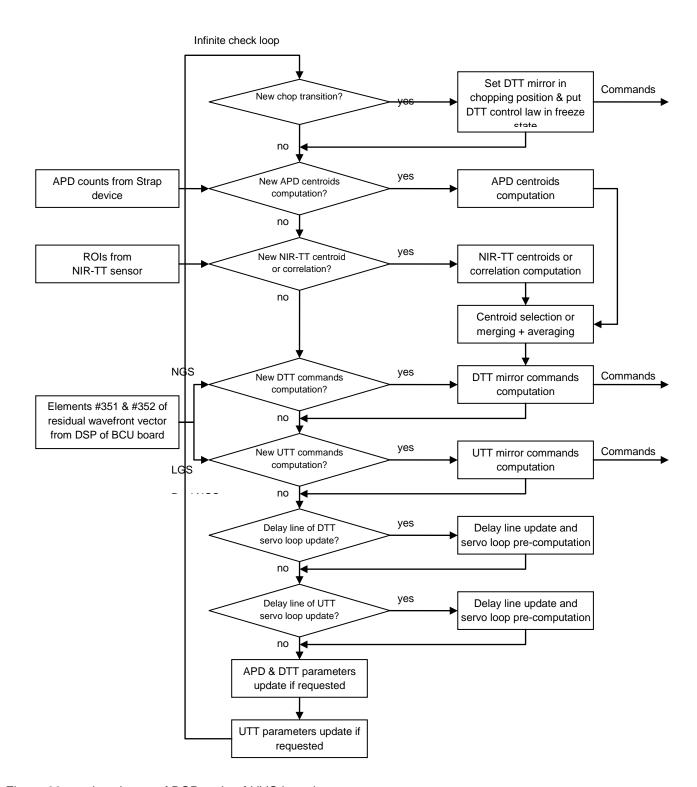

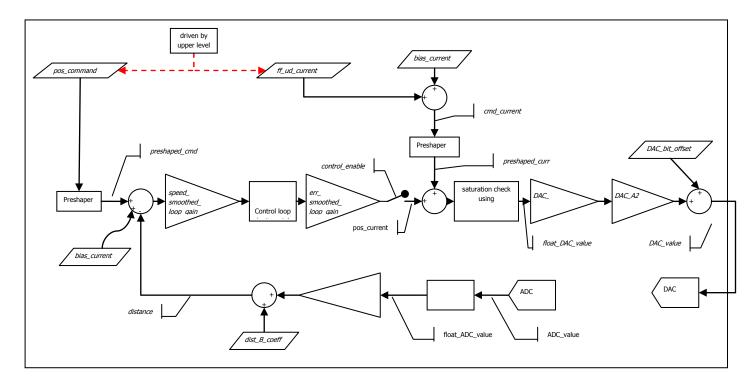

| Figure 39 - main scheme of DSP code of HVC board                                                          | 111 |

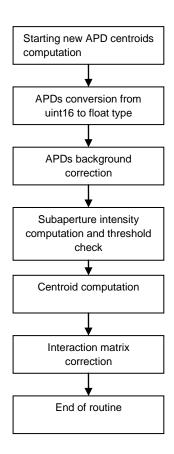

| Figure 40 - flow chart of APD centroids computation                                                       | 112 |

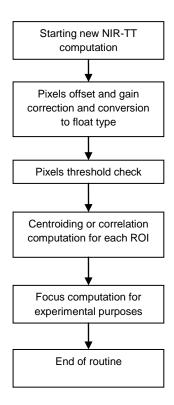

| Figure 41 - flow chart of NIR-TT centroids or correlation computation                                     | 113 |

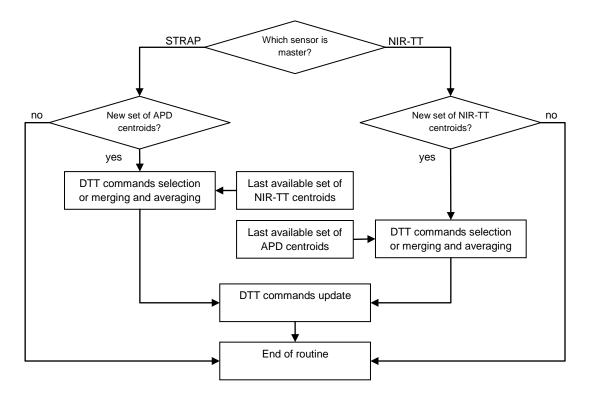

| Figure 42 - Flow chart of APD and NIR-TT outputs selection or merging and averaging                       | 114 |

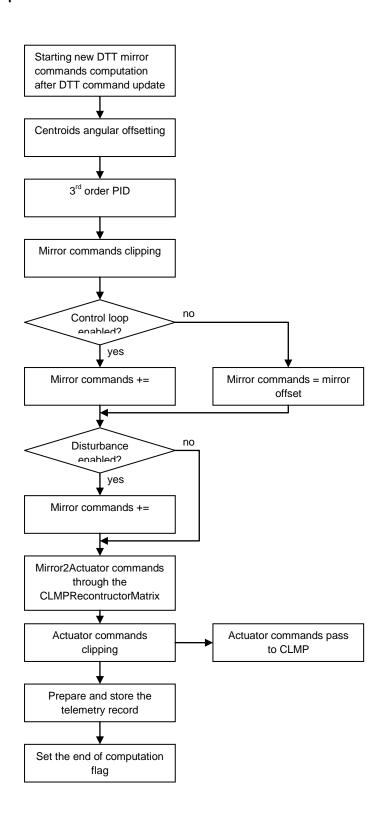

| Figure 43 - flow chart of DTT mirror commands computation                                                 | 115 |

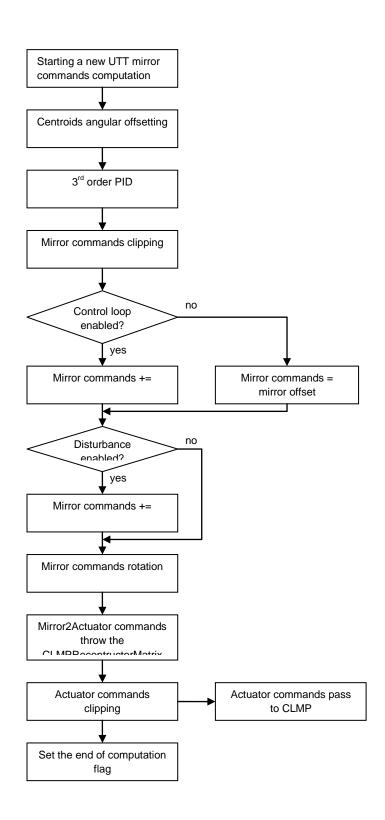

| Figure 44 - flow chart of UTT mirror commands computation                                                 | 116 |

| Figure 45 - CLMP loop flow chart                                                                          | 117 |

| Figure 46 – Chopping state machine                                                                        | 120 |

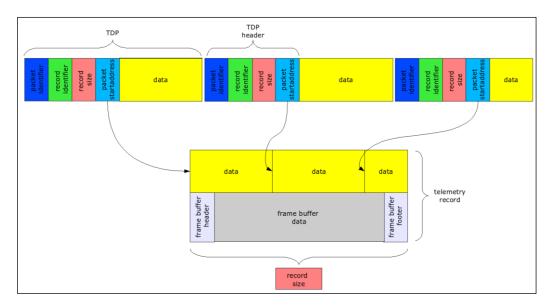

| Figure 47 – telemetry frame reconstruction                                                                | 136 |

| Figure 48 - MVME 6100 software block diagram                                                              | 140 |

Doc. : NGWFC\_RTC\_ASB\_002.doc Issue : 2 – March 28<sup>th</sup> , 2011

Page: 8 of 211

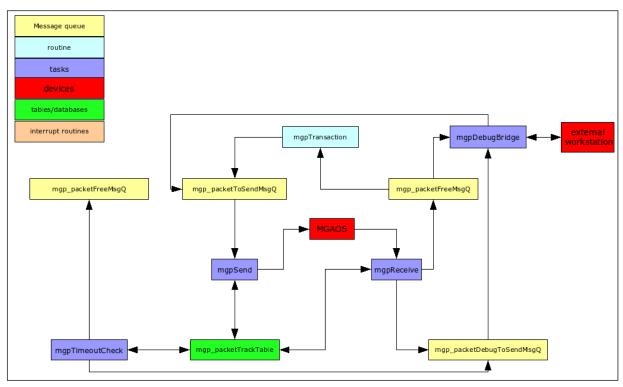

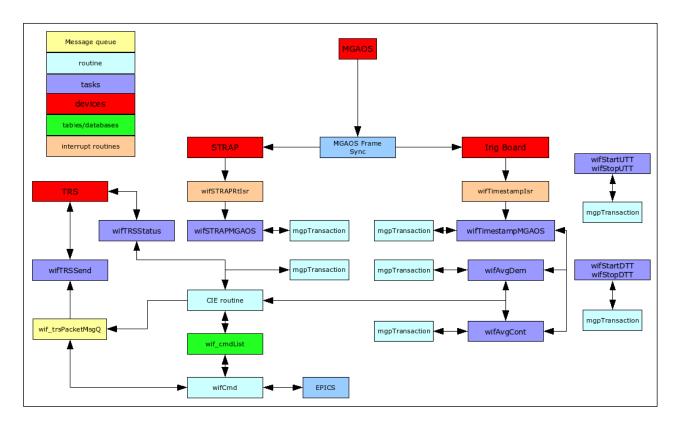

| Figure 49 - MVME 6100 mgp driver scheme   | 150 |

|-------------------------------------------|-----|

| Figure 50 - MVME 6100 wif software scheme | 153 |

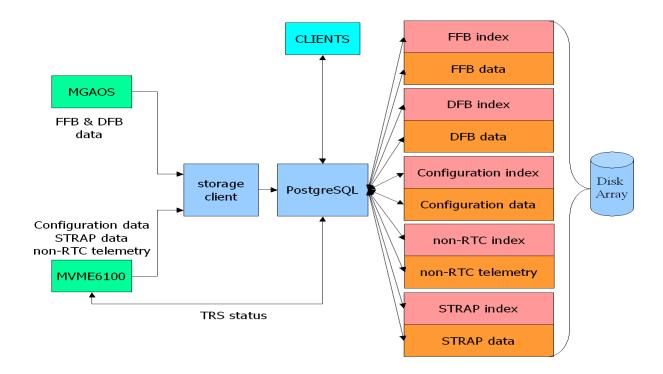

| Figure 51 - TRS generic data storage      | 154 |

Doc. : NGWFC\_RTC\_ASB\_002.doc Issue : 2 – March 28<sup>th</sup> , 2011

Page : 9 of 211

# **LIST OF TABLES**

| Table 1 – Flash memory mapping2                                                                                                                                                                                                                                                                                                            | 5 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Table 2 – BCU/Communication board supply distribution                                                                                                                                                                                                                                                                                      | 9 |

| Table 3 – Direct backplane bus signals                                                                                                                                                                                                                                                                                                     | 9 |

| Table 4 – Direct backplane bus signals                                                                                                                                                                                                                                                                                                     | 9 |

| Table 5 – DSP board supply distribution                                                                                                                                                                                                                                                                                                    | 9 |

| Table 6 – Tip-tilt mirror specifications4                                                                                                                                                                                                                                                                                                  | 5 |

| Table 7 – DTT mirror actuators driving voltages, slew rate and currents. RMS and min-max values for typica 'bad seeing' compensation4                                                                                                                                                                                                      |   |

| Table 8 – Apex PA243 amplifier main characteristics                                                                                                                                                                                                                                                                                        | 7 |

| Table 9 – HVC board supply distribution4                                                                                                                                                                                                                                                                                                   | 9 |

| Table 10 – System crate power dissipation summary 6                                                                                                                                                                                                                                                                                        | 8 |

| Table 11 – Voltages and currents of RTC power supply rails 6                                                                                                                                                                                                                                                                               | 9 |

| Table 12 – High voltage power supply unit requirements                                                                                                                                                                                                                                                                                     | 9 |

| Table 13 – Agilent N6700B specifications 6                                                                                                                                                                                                                                                                                                 | 9 |

| Table 14 – Internal HW interfaces. Power and logic                                                                                                                                                                                                                                                                                         | 3 |

| Table 15 – MGAOS supply and control connector pinout and specifications. Non listed pins are reserved 7                                                                                                                                                                                                                                    | 4 |

| Table 16 – Internal HW interfaces: communication                                                                                                                                                                                                                                                                                           | 5 |

| Table 17 – External HW interfaces: power                                                                                                                                                                                                                                                                                                   | 5 |

| Table 18 – External HW interfaces: data                                                                                                                                                                                                                                                                                                    | 5 |

| Table 19 – External HW interfaces: logic                                                                                                                                                                                                                                                                                                   | 6 |

| Table 20 – DTT mirror interface. The strain gage connection on the HVC board uses a different connector due to space constrains. To connect the actuator, we will use a dedicated cable adaptor with 1-to-1 connection to '00' and '0S' connectors, or, preferably, the connector on the actuator end will be replaced with a '00' series. | 7 |

| Table 21 – UTT mirror interface. The strain gage connection on the HVC board uses a different connector due to space constrains. To connect the actuator, we will use a dedicated cable adaptor with 1-to-1                                                                                                                                |   |

Doc. : NGWFC\_RTC\_ASB\_002.doc Issue : 2 – March 28<sup>th</sup> , 2011

Page: 10 of 211

|      | connection to '00' and '0S' connectors, or, preferably, the connector on the actuator end will be replaced with a '00' series.                                                                                                                      | 77          |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Tabl | e 22 – HVC board diagnostic interface. This interface is not used during standard operation, therefo is routed only to an internal connector on HVC analog board. It is possible however to bring the sig externally by means of a ribbon connector | gnals       |

| Tabl | e 23 – MGAOS electronics reliability prediction                                                                                                                                                                                                     | 80          |

| Tabl | e 24 – Complete RTC crate reliability prediction                                                                                                                                                                                                    | 81          |

| Tabl | e 25 – List of spares for 10 years of operation of two systems, 90% confidence                                                                                                                                                                      | 82          |

| Tabl | e 26 - Centroid computational time using the subaperture flux                                                                                                                                                                                       | 87          |

| Tabl | e 27 - Centroid computational time using the denominator free centroiding                                                                                                                                                                           | 87          |

| Tabl | e 28 - Timing of Step 6                                                                                                                                                                                                                             | 93          |

| Tabl | e 29 - Timing of Step 11                                                                                                                                                                                                                            | 102         |

| Tabl | e 30 - Timing description                                                                                                                                                                                                                           | 106         |

| Tabl | e 31 – WIF commands required for chopping operation                                                                                                                                                                                                 | 120         |

| Tabl | e 32 - DSP's memory organization                                                                                                                                                                                                                    | 122         |

| Tabl | e 33 – BCU DSP memory requirements                                                                                                                                                                                                                  | 122         |

| Tabl | e 34 – DSP Boards #0, #1 and #2 memory requirements                                                                                                                                                                                                 | 122         |

| Tabl | e 35 – HVC DSP memory requirements                                                                                                                                                                                                                  | <b>12</b> 3 |

| Tabl | e 36 – Pixel LUT content                                                                                                                                                                                                                            | 124         |

| Tabl | e 37 – Correlation algorithm efficiency comparison                                                                                                                                                                                                  | 125         |

| Tabl | e 38 – Computational and data transfer delay for different correlation cases and algorithms                                                                                                                                                         | 126         |

| Tabl | e 39 -Tip-tilt operating modes. The computation step refer to the algorithm description in §7.1.6.1.                                                                                                                                                | 127         |

| Tabl | e 40 - Telemetry buffer types                                                                                                                                                                                                                       | 132         |

| Tabl | e 41 - FFB record description                                                                                                                                                                                                                       | 133         |

| Tabl | e 42 - DFB record description                                                                                                                                                                                                                       | 134         |

| Tabl | e 43 - FC-UDP/IP encapsulation structure                                                                                                                                                                                                            | 135         |

| Tahl | e 44 - TCP-IP data structure for STRAP and Configuration streams (payload only shown here)                                                                                                                                                          | 136         |

Doc. : NGWFC\_RTC\_ASB\_002.doc Issue : 2 – March 28<sup>th</sup> , 2011

Page: 11 of 211

| Table 45 – MGP record structure                                           | 143 |

|---------------------------------------------------------------------------|-----|

| Table 46 - MGP packet structure                                           | 144 |

| Table 47 - MGP commands list                                              | 147 |

| Table 48 - MGP flags list                                                 | 148 |

| Table 49 - WIF_MGAOSREALTIMEPACKET                                        | 151 |

| Table 50 - WIF_STRAPREALTIMEPACKET                                        | 152 |

| Table 51 – MGAOS FFB stream                                               | 158 |

| Table 52 – MGAOS DFB stream                                               | 158 |

| Table 53 – NIR-TT DFB stream                                              | 158 |

| Table 54 – STRAP stream                                                   | 159 |

| Table 55 – NIR-TT stream                                                  | 159 |

| Table 56 – NONRTC stream                                                  | 160 |

| Table 57 – CONFIGURATION stream                                           | 160 |

| Table 58 - Internal SW interfaces                                         | 162 |

| Table 59 - External SW interfaces                                         | 162 |

| Table 60 - MGP_OP_RESET_DEVICES command: first control DWORD description  | 170 |

| Table 61 - MGP_OP_RESET_DEVICES command: second control DWORD description | 171 |

| Table 62 –COTS product list                                               | 205 |

Doc.: NGWFC\_RTC\_ASB\_002.doc Issue: 2 – March 28<sup>th</sup>, 2011

Page: 12 of 211

## 1 ACRONYMS

**AO** Adaptive Optics

**CCD** Charge Coupled Device

**CIE** Command Interpreter and Executer

**COTS** Commercial Off-The-Shelf

DDR Double Data RateDM Deformable MirrorDMA Direct Memory AccessDSP Digital Signal Processor

**DTT** Down Tip Tilt

**DTTM** Down Tip Tilt Mirror

FC-IP FibreChannel Internet Protocol

FITs Number of Failures in 10<sup>9</sup> hours

**FPDP** Front Panel Data Port

**GPIB** General Purpose Interface Bus

**HBA** Host Adapter Board

**HP** Width unit for 19" chassis, corresponding to 0.2" (5.08mm)

**HV** High Voltage

HVA High Voltage AmplifierHVC High Voltage Control

ICMP Internet Control Message Protocol

IIR Infinite Impulse Response

LFPM Linear Feet per Minute

LAN Local Area Network

LGS Laser Guide Star

LUT Look Up Table

MAC Multiply And Accumulate

mas milliarcseconds

MGAOS Microgate Adaptive Optics real-time System

MIMO Multiple Input Multiple Output

MIL-STD military standardMMF Multi-Mode Fiber

NDA Non Disclosure Agreement

NFS Network File System

NGS Natural Guide Star

**NGWFC** Next Generation Wavefront Controller

NIR-TT Near Infrared Tip-Tilt sensor

PCB Printed Circuit Board

**PIO** Programmable Input Output

**PSU** Power Supply Unit

Doc.: NGWFC\_RTC\_ASB\_002.doc Issue: 2 – March 28<sup>th</sup>, 2011

Page: 13 of 211

RMS Root-Mean-Square

RTC Real Time Controller

SAN Storage Area Network

SAS Serial Attached SCSI

SCSI Small Computer System Interface

SFP Small Form factor Pluggable

SI The International System of Units

SH Shack-Hartmann

**SRAM** Static Random Access Memory

**SDRAM** Synchronous Dynamic Random Access Memory

**STRAP** System for Tip-tilt Removal with Avalanche Photo-diodes

TBC To Be ConfirmedTBD To Be Defined

TDP Telemetry Data Packet

TRS Telemetry Recorder/Server

**U** Height unit for 19" chassis, corresponding to 1.75" (44.45mm)

**UTT** Uplink Tip Tilt

UTTM Uplink Tip Tilt MirrorVME VersaModule EurocardWBS Work Breakdown Structure

WCP Wavefront Controller Command Processor

**WIF** Wavefront Controller Interface

WFP Wavefront processor

WFS Wavefront Sensor

Doc.: NGWFC\_RTC\_ASB\_002.doc Issue: 2 – March 28<sup>th</sup>, 2011

Page: 14 of 211

## 2 APPLICABLE DOCUMENTS

- [AD1] CARA/W.M. Keck NGWFC RTC Requirements – Keck Adaptive optics note #311. Version 1.0, March 11<sup>th</sup>, 2005

- [AD2] CARA/W.M. Keck NGWFC RTC Tip-Tilt Requirements – Keck Adaptive optics note #329. Version 1.0, May 25<sup>th</sup>, 2005

- [AD3] CARA/W.M. Keck NGWFC RTC Vendor Statement of Work – Keck Adaptive optics note #310. Version 1.0, March 11<sup>th</sup>, 2005

- [AD4] CARA/W.M. Keck NGWFC System Design Manual – Keck Adaptive optics note #289. Version 2.0, August 15<sup>th</sup>, 2005

- [AD5] Microgate S.r.l.

Real Time Controller Preliminary Design Review Data Package

Issue 1 August 22<sup>nd</sup>, 2005

- [AD6] CARA/W.M. Keck Request for change to the NGWFC RTC: Post PDR updates - Keck Adaptive optics note #354. Version 1.4, November 3<sup>rd</sup>, 2005

- [AD7] CARA/W.M. Keck NGWFC RTC Acceptance Test Plan - Keck Adaptive optics note #374

- [AD8] CARA/W.M. Keck NGWFC Detailed Design Report - Keck Adaptive optics note #371 December 2<sup>nd</sup>, 2005

- [AD9] Microgate S.r.l.

Real Time Controller Detailed Design Review Data Package

Issue 1 December 2<sup>nd</sup>, 2005

- [AD10] Microgate S.r.l. NGWFC Test\_Report 07/02/06 and 07/11/06, Issue 1 – July 11<sup>th</sup>, 2006

- [AD11] Microgate S.r.l.

memory map Keck\_NGWFC 1\_05.xls

Spreadsheet containing the control system memory mapping.

Issue 1.05, September 2007

- [AD12] CARA/W.M. Keck Statement of Work For: Modifications to the Keck AO NGWFC to Support the Near-Infrared Tip-Tilt Sensor Project – Keck Adaptive optics note #824. Version 0.4, March 22<sup>nd</sup>, 2011

Doc.: NGWFC\_RTC\_ASB\_002.doc Issue: 2 – March 28<sup>th</sup>, 2011

Page: 15 of 211

[AD13] CARA/W.M. Keck

Near-Infrared Tip-Tilt Sensor Detector Readout Scheme – Keck Adaptive optics note #xxx. Version 1.6, March  $17^{th}$ , 2011

[AD14] Microgate S.r.l.

WIFCommandList\_11.xls Spreadsheet containing the WIF command list. Issue 11, March 2011

Doc. : NGWFC\_RTC\_ASB\_002.doc Issue : 2 – March 28<sup>th</sup> , 2011

Page: 16 of 211

## 3 REFERENCE DOCUMENTS

| [RD1] | R. Biasi, M.Andrighettoni et al 'Dedicated flexible electronics for adaptive secondary control', SPIE Proc. on 'Advancements in Adaptive Optics', 5490, p.1502 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [RD2] | E-mails exchanged between Microgate and CARA-Keck between April 21st ad May 7th, 2005                                                                          |

| [RD3] | Department of Defense USA, MIL-HDBK-217 Revision F, Reliability Prediction of Electronic Equipment                                                             |

| [RD4] | Keck AO Wavefront Control – Hardware Manual                                                                                                                    |

| [RD5] | INCITS - FibreChannel – Physical and Signaling Interface – ANSI – INCITS 230-1994                                                                              |

| [RD6] | M. Rajagopal, R. Bhagwat, W. Rickard - RFC 2625 - IP and ARP over FibreChannel - June 1999                                                                     |

Doc. : NGWFC\_RTC\_ASB\_002.doc Issue : 2 – March 28<sup>th</sup> , 2011

Page: 17 of 211

## 4 INTRODUCTION

This document contains the As Built Data Package of those parts of the NGFWC Real Time Controller that are under responsibility of Microgate.

The document derives directly from the Detailed Design Review report ([AD9]).

Even if the entire document has been thoroughly reviewed, addressing in particular performance analysis and design details, we report hereafter a list of the major additions and modifications with respect to the original document.

- Reset circuitry description . The reset handling circuit was moved from the VME backplane to the MGAOS crate

- Assessment of hardware interfaces

- Chopping functionality

- CLMP loop tuning

- Software design

- WIF-WCP interface

- Command Interpreter and Executer

- TRS database (here we introduced a major change with respect to PDR)

- Results of preliminary tests on TRS performance

- Validation of real-time computation performance estimate through testing of algorithms and C versus assembler comparison

- Assessment of interface test between RTC and TRS including test of IP over FibreChannel communication

The document has been further updated (Issue 2) to comprehend the interface to the new Near Infrared Tip-Tilt (NIR-TT) camera. This part of the design is currently at PDR level. The affected sections are listed in the Change Record.

An 'Annex' section has been added at the end of the document, including:

- Low level MGAOS/MVME communication protocol (MGP)

- Final choice of COTS components (jointly with CARA)

- Schematics of all proprietary boards, including component placement and bill of material (these are reported as links to external documents)

Doc.: NGWFC\_RTC\_ASB\_002.doc Issue: 2 – March 28<sup>th</sup>, 2011

Page: 18 of 211

#### 5 SYSTEM OVERVIEW

In this section we present a general overview of the NGWFC RTC design.

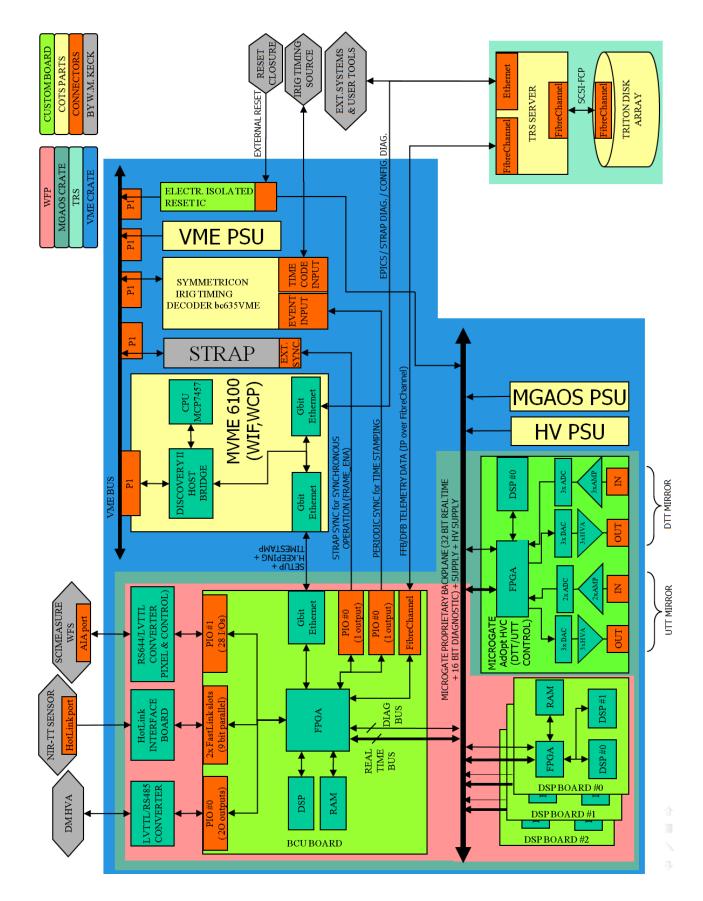

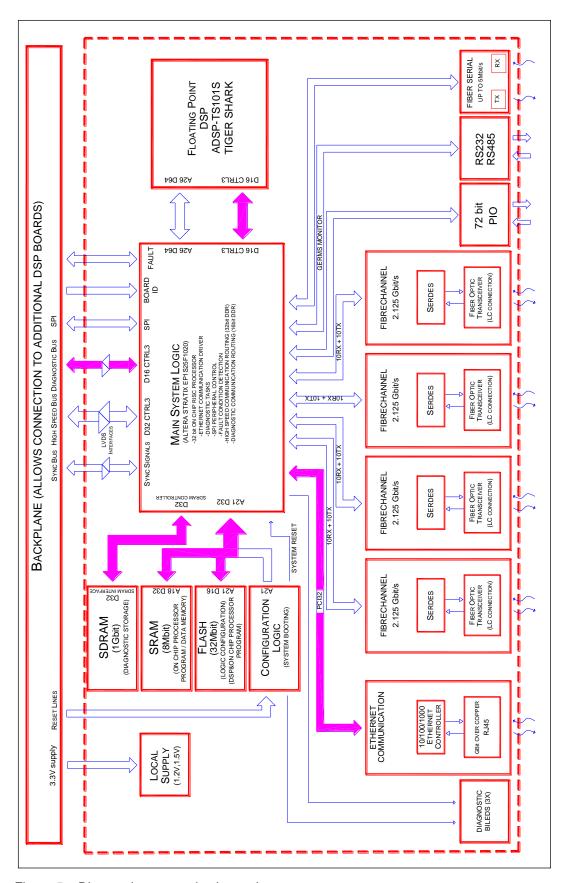

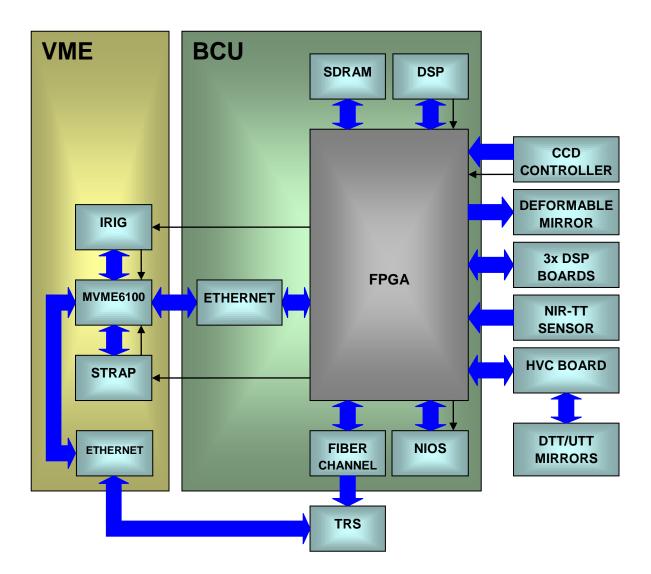

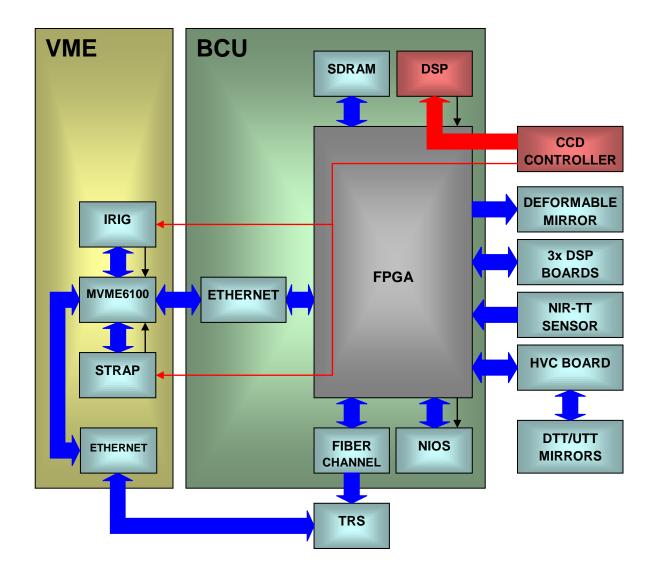

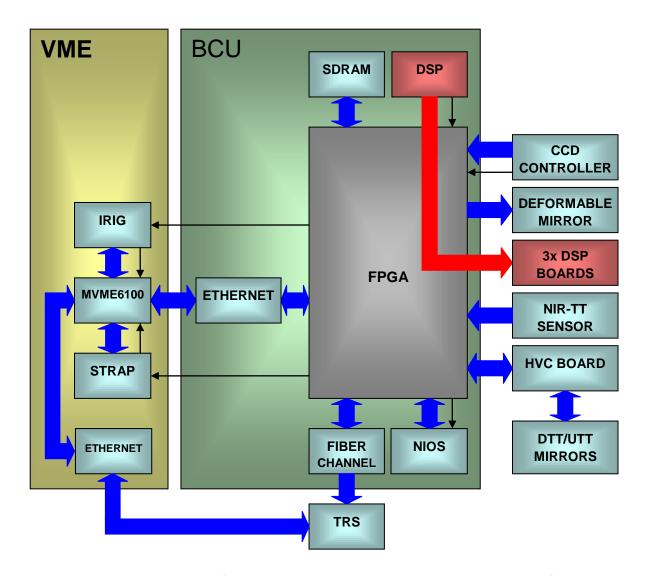

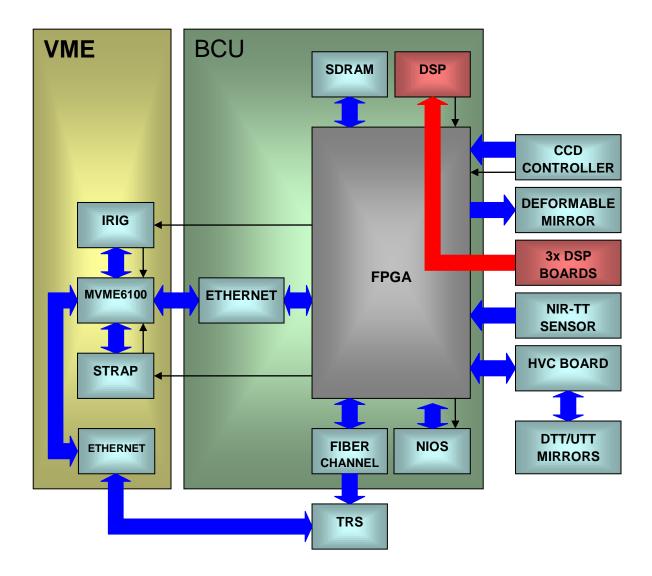

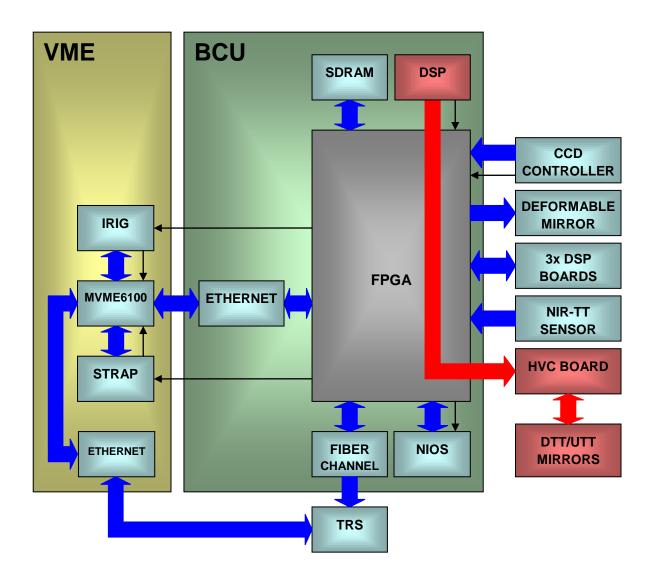

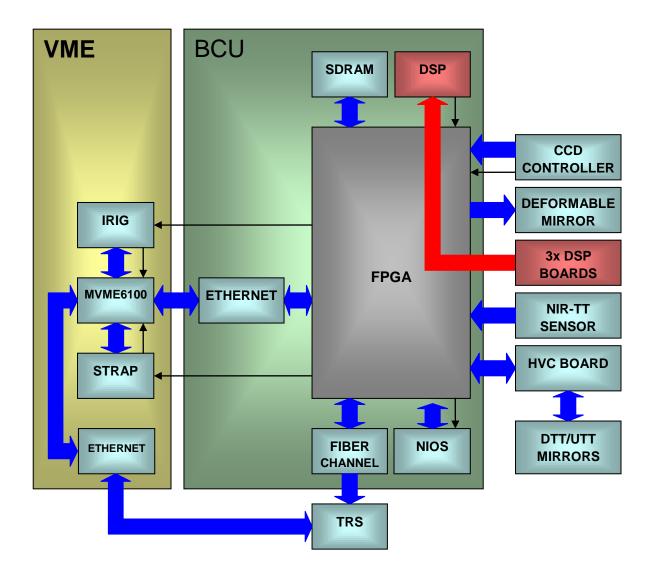

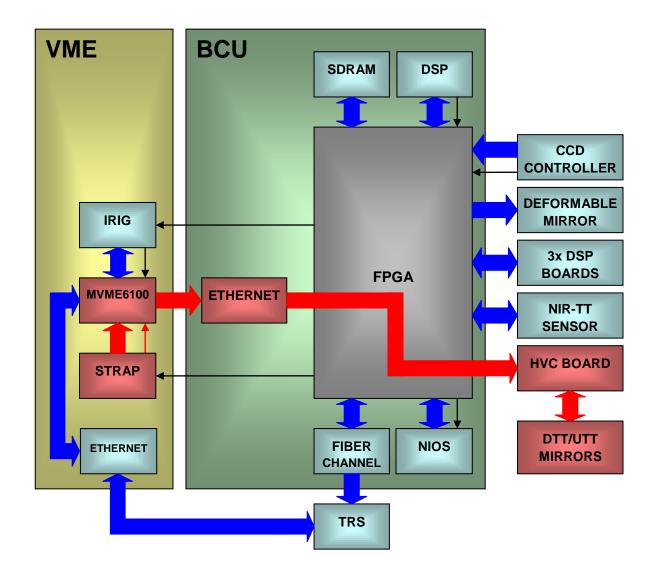

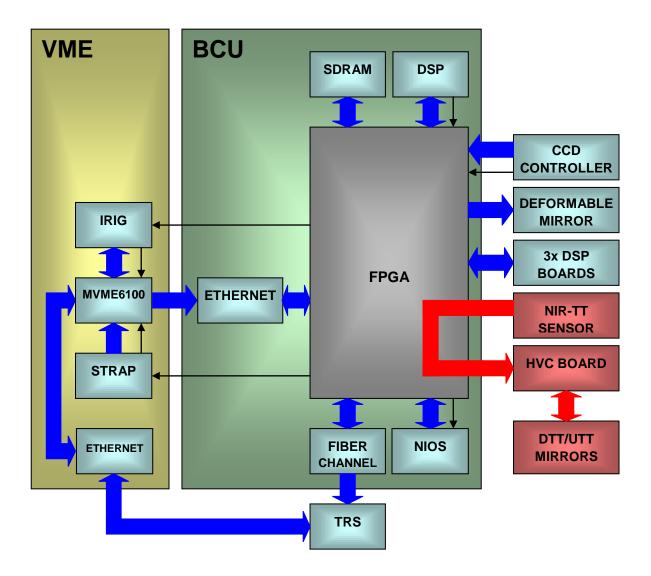

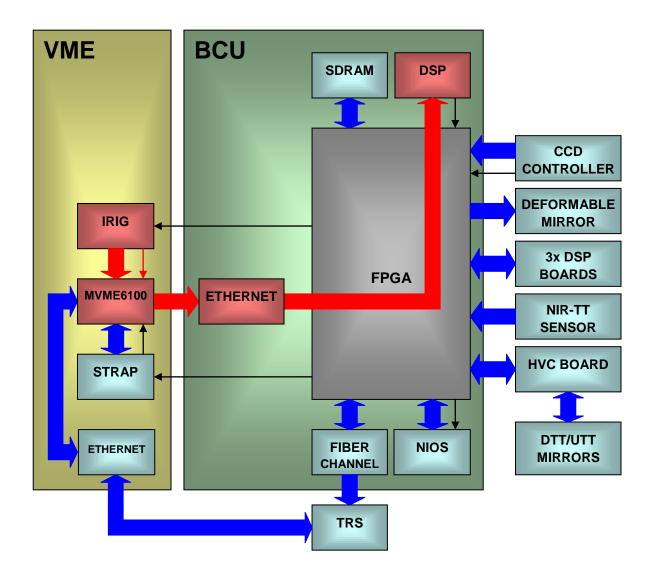

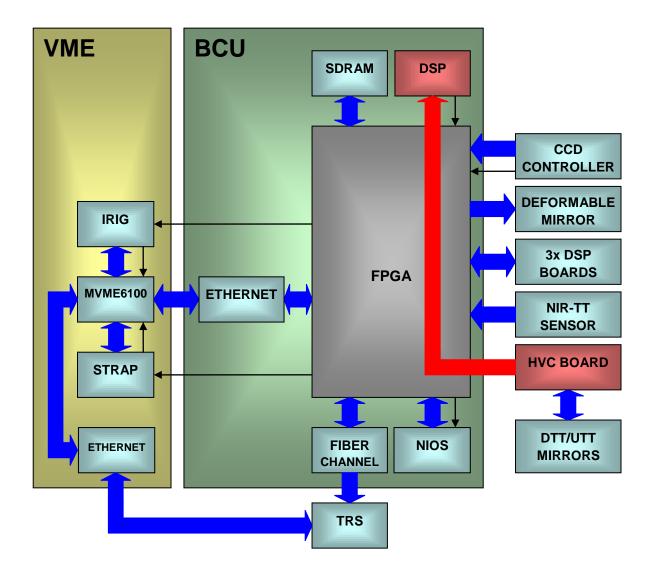

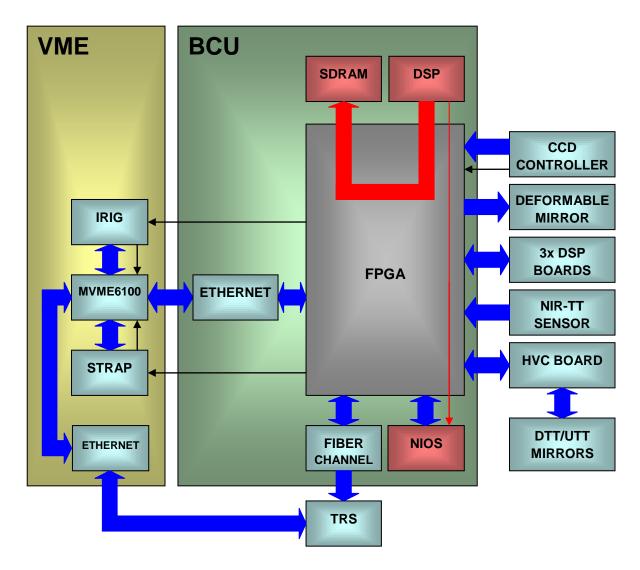

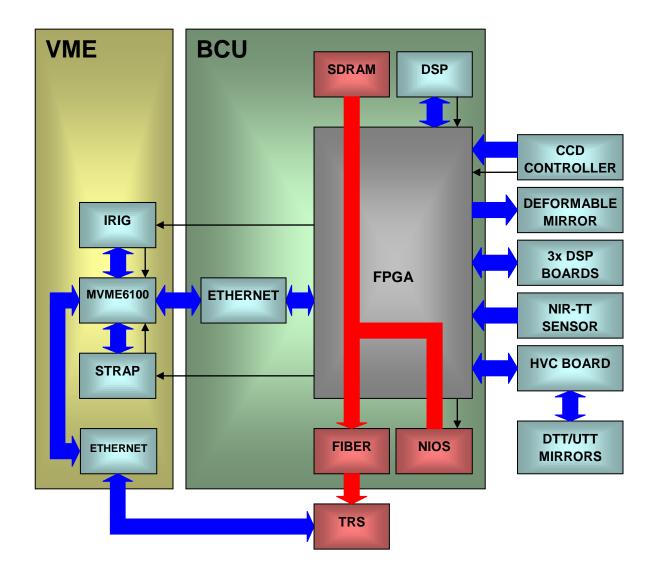

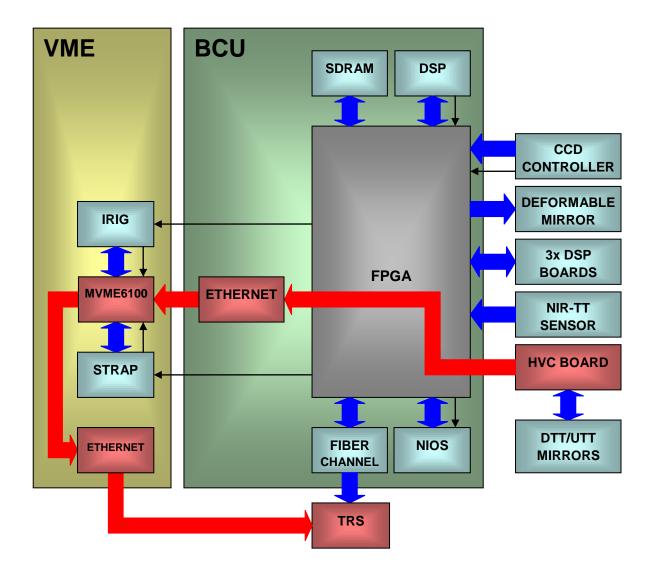

In Figure 1 we present a global block diagram of the designed architecture.

The main system functional blocks of NGWFC RTC are:

- WaveFront Processor (WFP): it is the hearth of the wavefront controller, performing all real-time computations from pixel acquisition to generation of commands for the DM and DTT/UTT mirrors.

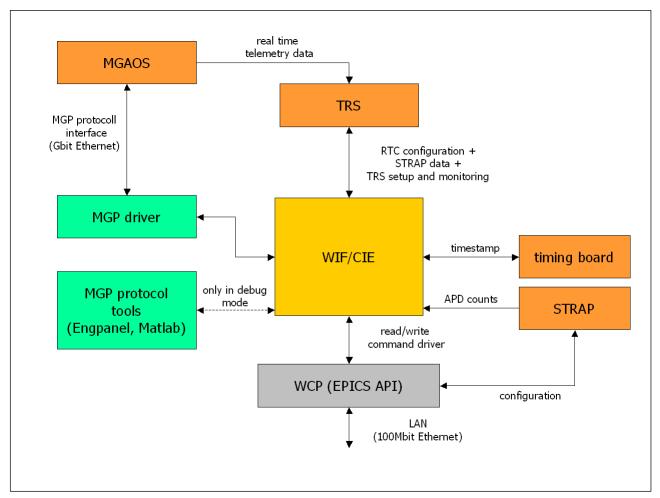

- Wavefront controller Interface (WIF): this is the interface between external commands (from WCP) to the WFP.

- DTT/UTT controllers, implementing closed loop control of the piezoelectric-actuated DTT and UTT mirrors.

- STRAP tip-tilt sensor and controller.

- Telemetry Recorder Server (TRS): it is the main diagnostic storage system, receiving streams of data from WFP, STRAP, WIF and WCP.

All this components can be clearly distinguished in the block diagram of Figure 1, describing also the hardware devices and interfaces where the functions above are actually implemented.

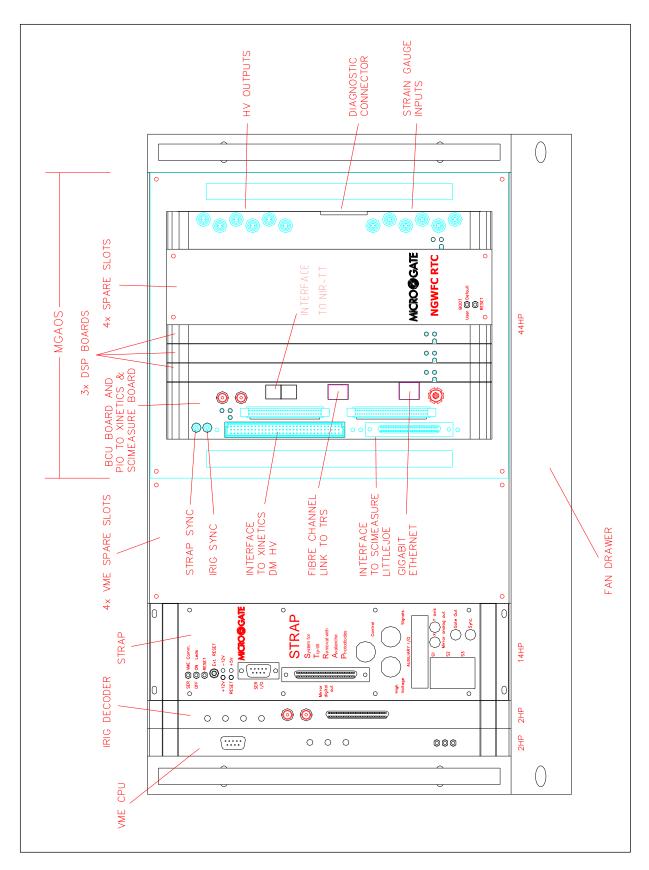

The *WFP* is implemented by the Microgate Adaptive Optics real-time System (MGAOS). This is a proprietary hardware architecture that was developed in the frame of other adaptive optics projects, with the aim of providing a well-optimized and scalable high performance computational and control architecture. All MGAOS components are mounted on a single proprietary bus and the whole system is fit into a small case integrated in the VME crate (see Figure 2). The MGAOS is directly interfaced to the Wavefront Sensor Camera (standard AIA interface) and to the DM HVA (FPDP-like interface). The *DTT/UTT controllers* are also integrated in the MGAOS, thus a direct interface between MGAOS and DTT/UTT mirrors is provided.

The **WIF** is implemented on a standard VME architecture (PowerPC VME 6100 CPU board). The WIF is the interface between WCP and WFP. It also acts as supervisor of all RTC operations. In particular, all setup and configuration of MGAOS are performed by the VME CPU through a private Gbit Ethernet connection. The same interface allows also transferring real-time data from **STRAP** to MGAOS.

The *TRS* comprehends a storage data server and a large disk array for data storage, capable of storing the system telemetry for longer than five observing nights. It is interfaced to MGAOS through a dedicated FibreChannel link, through which all bulky telemetry data are transferred. STRAP and configuration diagnostics is transferred directly from the VME CPU via a standard Gbit Ethernet LAN. The client workstation can query the TRS by means of the same standard LAN.

An IRIG board installed on the VME crate provides system synchronization to an absolute timing reference. An external reset line allows to reset the RTC remotely.

Doc.: NGWFC\_RTC\_ASB\_002.doc Issue: 2 – March 28<sup>th</sup>, 2011

Page: 19 of 211

Figure 1 - NGWFC RTC global architecture

Doc.: NGWFC\_RTC\_ASB\_002.doc Issue: 2 – March 28<sup>th</sup>, 2011

Page: 20 of 211

Figure 2 – NGWFC RTC: VME and MGAOS crate mechanical layout

Doc. : NGWFC\_RTC\_ASB\_002.doc Issue : 2 – March 28<sup>th</sup> , 2011

Page: 21 of 211

## **6 HARDWARE DESIGN**

In this section we describe the HW design of the NGWFC RTC. To this aim, the main system components are analyzed, namely WIF/WFP hardware, TRS and storage disk array. The subsystem main components, in particular the boards comprehended in the MGAOS system, are described in detail. We analyze also the design/simulation/prototyping results of DTT/UTT HVC board. The design process of this dedicated hardware component has been completed, including experimental tests on a single-channel breadboard. The construction will start immediately after DDR.

Finally, we describe the internal and external system interfaces.

#### 6.1 WIF/WFP Hardware

The WFP is the real-time part of the NGWFC RTC. It acquires the pixels data from the WFS, computes the centroids, generates the residual wavefront and generates the commands for both deformable mirror and DTT/UTT tip-tilt mirrors.

The WIF is the interface between the real-time system and WCP.

Both WIF and WFP hardware are hosted on a single crate, where we can distinguish the following main components:

- Microgate crate (MGAOS), comprehending also the interfaces to WFS, DM drive and DTT/UTT mirrors. All strictly real-time WFP functions are implemented by the MGAOS

- Host VME CPU board

- IRIG timing board

- STRAP

- Power supply system

## **6.1.1 Microgate Adaptive Optics crate (MGAOS)**

The MGAOS implements all real time functions of the WFP. The system is based on the Microgate proprietary 'AdOpt' hardware. The proposed configuration comprehends:

- 1 AdOpt BCU board (§6.1.1.1), implementing several functions:

- input real-time interface to the SciMeasure controller

- pixel background and flat field compensation

- centroid computation

- output real-time interface to the Xinetics controller

- bus arbiter and master of the data exchange between different processors on the backplane (in particular, transferring centroids to the DSP boards and retrieving DM commands)

Doc. : NGWFC\_RTC\_ASB\_002.doc Issue : 2 – March 28<sup>th</sup> , 2011

Page: 22 of 211

- interface to the VME crate for real-time data transfer of STRAP data and system setup,

through a dedicated Gbit Ethernet port

- telemetry data interface to the TRS through FibreChannel port

- 3 AdOpt DSP boards (§6.1.1.2), each comprehending 2 TigerSharc DSPs (ADSP TS101) with 300 MHz internal clock rate, capable of 0.6 Giga-floating point multiply-and-accumulate per second (sustained performance, each DSP). The DSP boards implement the most extensive computational tasks, namely the residual wavefront computation and the control law servo computation.

- 1 AdOpt HVC board (§6.1.1.3), capable of controlling digitally in closed loop up to six axes based on piezoelectric transducers with strain gauge position feedback. The HVC board is used to drive directly both the DTT and UTT mirrors.

- Passive proprietary backplane (§6.1.1.4), based on B-LVDS technology. This is the backbone of each half-crate. Power supply, diagnostic signals, real time communication and diagnostic communication are distributed by the backplane. The backplane can host up to 12 boards, while the current configuration uses 7 slots.

- Reset Circuitry to handle properly the external reset, the VME reset and the local reset pushbutton (§6.1.1.5)

The design philosophy of the AdOpt components is aimed to realize a very efficient real-time parallel computer, with particular focus on inter-processor communication.

In the following sections we describe in more detail the architecture of the main MGAOS components.

#### 6.1.1.1 AdOpt BCU board

The BCU (Basic Computational Unit) board is a general purpose board, capable of different tasks within an adaptive optics system. It is mainly dedicated to route and manage the communication within a single Microgate AdOpt crate or among several crates or subsystems.

In the NGWFC RTC application, the BCU acts as sequencer of the different computational tasks, it manages the real-time data exchange among the MGAOS DSPs and handles the telemetry buffering and interface.

The on-board DSP handles the pixel background, flat field compensation and centroids computation tasks.

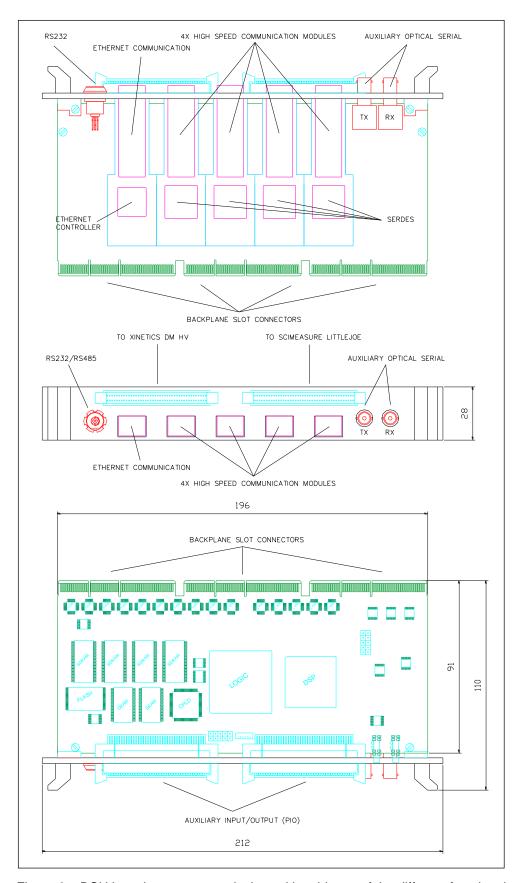

In the following section we give an overview of the main board components. A block diagram of the BCU is presented in Figure 3.

Doc. : NGWFC\_RTC\_ASB\_002.doc lssue : 2 – March 28<sup>th</sup> , 2011

Page: 23 of 211

Doc.: NGWFC\_RTC\_ASB\_002.doc Issue: 2 – March 28<sup>th</sup>, 2011

Page: 24 of 211

Figure 3 - BCU board block scheme

#### 6.1.1.1.1 Main system logic

The Main System Logic is realized with an Altera Startix EP1S25F1020 programmable logic. It performs the following main tasks:

- interface between all on board devices;

- interface with the backplane buses;

- interface to the PIO (see 6.1.1.1.11). This ports provides a versatile interface to different devices. In our application it is used to read frames from the WFS and to send commands to the DM HVA

- on chip 'soft' processor (Altera Nios II), which performs:

- driver of the Ethernet diagnostic link

- acquisition of all local diagnostic devices (board temperatures)

- transfers telemetry data from DSPs to SDRAM and then to TRS

#### 6.1.1.1.2 Main real time computational unit

The computational unit is based on one ADSP-TS101S DSPs.

The DSPs communicate with the main logic by two shared buses and some direct lines:

- the high speed bus has 64 data bits at ~60MHz of frequency with a typical throughput of 4Gbit per second;

- the diagnostic bus uses two 8 data bits parallel serial lines (called link ports) in DDR mode at ~60MHz of frequency, with a typical throughput of 2Gbit per second;

- additional ports are used by the system logic to synchronize the DSP operation with the external tasks

Within the MGAOS, the BCU DSP performs pixel background, flat field compensation and centroid computation.

## 6.1.1.1.3 Reconfiguration logic

The reconfiguration logic is realized with an Altera EPM3128. It is a non volatile programmable logic which has the task of downloading the configuration of the main logic and the main logic on-chip processor code from the non volatile Flash.

A safety mechanism is provided in order to guarantee that the system can be always recovered from any wrong configuration. The configuration process runs according to the following steps:

- after reset, the configuration logic starts reading the 'user' configuration from the Flash memory

- if the user configuration is not recognized by the logic as a valid configuration (validation mechanisms are factory embedded in the logic configuration loading circuitry), the configuration logic automatically loads the default configuration. This configuration is stored into a protected

Doc. : NGWFC\_RTC\_ASB\_002.doc Issue : 2 – March 28<sup>th</sup> , 2011

Page: 25 of 211

area of the Flash memory. Thus, it is not possible to damage accidentally the default configuration through the Ethernet connection.

• If the user configuration is recognized by the system logic as a valid configuration, but it does not work properly (as it might happen frequently during system debug), it is possible to force the default configuration by means of a dedicated hardware signal, which is available to the user (bus boot select)

The configuration logic also manages all the reset signals to all the devices that could be reset: Flash, main logic, DSP and Ethernet chip.

#### 6.1.1.1.4 Non volatile storage memory (FLASH)

The non volatile memory is necessary at system booting to configure the system. The memory used is a typical flash memory with a programmable write locked area with a total size of 32Mbit.

The main logic configuration and the on-chip program code are duplicated into two different areas: the **default** and **user** area.

The default configuration and program are placed in the locked area to avoid accidental overwriting. This configuration permits to restart the system if the user configuration or program code have been corrupted or they don't work properly.

The selection of the booting mode is done either automatically, if the user mode configuration fails, or by the external hardware signal bus\_boot\_select.

The DSP program code area contains the DSP program. It can be automatically downloaded at system booting. In the MGAOS application, however, it is foreseen to upload the DSP code from an external database at every system startup. This task is performed by the VME CPU.

The configuration parameters is a fixed area which contains all the software parameters that define the system board configuration after start up. They are programmable using the diagnostic interface (Ethernet) and are maintained until new configuration parameters are written.

The flash memory is organized as follow:

| Start address(byte) | size(byte) | locked | Description                      |

|---------------------|------------|--------|----------------------------------|

| 0x000000            | 0x180000   | yes    | main logic default configuration |

| 0x180000            | 0x040000   | yes    | on-chip default program code     |

| 0x1C0000            | 0x040000   | no     | on-chip user program code        |

| 0x200000            | 0x180000   | no     | main logic user configuration    |

| 0x380000            | 0x070000   | no     | not used area                    |

| 0x3F0000            | 0x00A000   | no     | configuration parameters         |

| 0x3FA000            | 0x006000   | no     | not used area                    |

Table 1 - Flash memory mapping

The connection between the main logic and the flash it realized by a 16bit data bus at 60 MHz of frequency with a typical throughput of 1Gbit per second. This bus is shared with the SRAM bus because, usually, the flash device is used just at start up.

Doc.: NGWFC\_RTC\_ASB\_002.doc Issue: 2 – March 28<sup>th</sup>, 2011

Page: 26 of 211

#### 6.1.1.1.5 SRAM memory

The 8Mbit SRAM memory is dedicated only to the main logic on-chip program and data memory. The organization of the memory depends on the on-chip program code.

The connection between the main logic and the SRAM is realized by a 32bit data bus at 60 MHz of frequency with a typical throughput of 2Gbit per second. This bus is shared with the FLASH device because during ordinary operation the FLASH is never used and then the bus is free to be used with the SRAM.

#### 6.1.1.1.6 SDRAM memory

A bulk memory is provided on the BCU board for diagnostic data storage. The bulk memory available is 1Gbit. The bulk memory is directly connected to the main system logic. It can be accessed directly by the embedded diagnostic processor and, via system logic, by the DSP. The SDRAM is connected to system FPGA by means of a 32 bit bus at 60 MHz with to Gbit/s bandwidth.

#### 6.1.1.1.7 High speed backplane bus

The high speed backplane bus has been designed to allow the connection between the BCU board and all the control boards. The backplane bus is based on a strict master - slave architecture where the BCU board is the master and starts the transaction sending to the all control boards a request. Depending on the request all DSP and HVC boards react and can either receive the data sent by the BCU board (data write to the DSP board), or they can take the control of the bus if data have to be sent back to the BCU board.

The high speed backplane bus controller is performed by the main logic which redirects all the data from or to this bus to the high speed communication link interface.

The bus is physically based on BLVDS devices. This architecture guaranties signal integrity with high density and high speed busses.

The high speed backplane bus is a 32bit data bus at 60MHz in DDR mode with a typical throughput of 4Gbit per second.

#### 6.1.1.1.8 Diagnostic backplane bus

The diagnostic backplane bus has been designed with a very similar architecture of the high speed backplane bus. It is controlled by the main logic which redirects all the data from or to this bus to the diagnostic communication link.

The diagnostic backplane bus is a 16bit data bus at 60MHz in DDR mode with a typical throughput of 2Gbit per second with a double speed with respect to the Ethernet diagnostic communication link. This choice has been taken to have a large margin between the internal bandwidth and the external one.

#### 6.1.1.1.9 High speed communication links

Doc.: NGWFC\_RTC\_ASB\_002.doc Issue: 2 – March 28<sup>th</sup>, 2011

Page: 27 of 211

The high speed communication allows to exchange data between different BCU boards or between BCU and external devices. In the NGWFC RTC, one high speed communication channel is used to transfer telemetry data from the BCU board to the TRS.

Every high speed communication channel is based on a full-duplex fiber optic link operating at 2.125 Gbit/s, according to the 2 Gbit/s FibreChannel physical layer standard.

Up to four high speed communication modules can be installed on the board. The number and the logic function of each channel can be configured according to the particular need.

The modules are based on the Agilent HFBR 5923 optical transceiver module (or equivalent). The module is compatible with industry standard LC-duplex fiber optic connectors, and is compatible with both 62.5-125 $\mu$ m and 50-125 $\mu$ m Multi Mode Fibers. The maximum specified link length is 150m with 62.5-125 $\mu$ m fiber and 300m with 50-125 $\mu$ m MMF.

#### 6.1.1.1.10 Diagnostic communication link

The diagnostic communication is intended to be used for different purposes:

- transferring the diagnostic information (like acquired circular buffers and statistics);

- sending commands and acquiring system status;

- perform system maintenance.

The diagnostic communication link is based on a standard Ethernet interface, operating at 10/100/1000 Mbit/s. The physical interface is based on the standard copper link, with standard RJ 45 connector.

#### 6.1.1.1.11 Expansion programmable input/output ports

The BCU/Communication boards comprehends a flexible expansion port (referenced as PIO – Programmable Input Output port) that can be used for interfacing different devices. The expansion ports comprehends 72 reconfigurable digital I/O lines, that can be configured according to different hardware interfacing standards (LVTTL, SSTL-2, SSTL-3, LVDS, ...). The I/O lines are directly connected to the system logic (FPGA), and are available on the BCU front panel, on two 80 pins high density ribbon connectors (type 3M 810 series).

Within the MGAOS, the both PIO ports are used:

- PIO #0 implements the interface to the DM HVA. A simple interface board to convert the signal levels from LVTTL (PIO) to RS485 (DM HVA).

- PIO #1 implements the interface to the WFS. A simple interface board to convert the signal levels from RS644 (SciMeasure Little Joe AIA interface) to LVTTL (PIO).

- Two additional signals on PIO #0 are used to generate the synchronization signals for STRAP and IRIG board.

In both cases, the interfaces greatly benefit from the direct FPGA connection. In fact the FPGA handles directly the data transfers, thus offloading completely the DSP. The transfer between logic and DSP occurs by means of a true DMA process.

Doc.: NGWFC\_RTC\_ASB\_002.doc Issue: 2 – March 28<sup>th</sup>, 2011

Page: 28 of 211

#### 6.1.1.1.12 Serial links

Two standard serial communication links are available on the BCU board:

- one link is used to control and check the main logic functionalities and on-chip program flow during the system software development. This link is not used during normal operation of the system.

- the second link is available on front panel and can be used as general purpose serial interface. The

serial port can be externally configured (by a configuration pin) according to RS232 or RS485

standard by means of a configuration pin. The maximum communication speed is up to 1 Mbit/s.

There is no use foreseen for this port in the MGAOS.

#### 6.1.1.1.13 'Slow' fiber input/output

An additional fiber link is available on the BCU board. This port can be used for different purposes:

- asynchronous serial interface with speed up to 5 Mbit/s

- bi-directional transmission of logic signals, e.g. for synchronization purposes.

The fiber optic interface has ST standard connectors. The transmitter/receiver sections are based on Agilent HFBR 1412/2412 devices. One important feature is that the optical interface is 'static', i.e. there is no lower speed limit for the information or signals to be transmitted.

In the present design, there is no use foreseen for the 'slow' fiber interface.

## 6.1.1.1.14 Power supply

The BCU board requires a single 3.3V @ 3A (typical) supply. Internally, additional supply voltages are required for board operation, in particular 1.2V and 1.5V at relatively high currents for the DSP and FPGA cores respectively. The high accuracy, low impedance requirements on these power rails can be more easily satisfied if a distributed supply concept is adopted, where these low voltages are generated on-board by means of high efficiency, fast switching DC-DC converters.

The internal supply distribution scheme is resumed in Table 2.

Doc. : NGWFC\_RTC\_ASB\_002.doc Issue : 2 – March 28<sup>th</sup> , 2011

Page: 29 of 211

| Supply of:              | Voltage | Current | Generated by:                                         |

|-------------------------|---------|---------|-------------------------------------------------------|

| DSP core                | 1.2V    | 1.2A    | On-board switching DC-DC converter, derived from 3.3V |

| FPGA core               | 1.5V    | 0.8A    | On-board switching DC-DC converter, derived from 3.3V |

| Logic, BLVDS            | 3.3V    | 0.85A   | 3.3V (VCC)                                            |

| Gigabit Ethernet module | 3.3V    | 1.2A    | 3.3V (VCC)                                            |

| FibreChannel modules    | 3.3V    | 0.8A    | 3.3V (VCC)                                            |

Table 2 – BCU/Communication board supply distribution

#### 6.1.1.1.15 Direct backplane bus signals

From the backplane bus there are some directs signals controlling some hardware configurations or time critical events. The following table summarize these signals:

| Name              | Direction    | Description                                                                                                                                                                                                                                        |

|-------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bus_power_fault   | in/out       | typically configured as an input to verify if an external power fault condition happens. If a fault condition happens inside the board the signal is driven as an output by the main logic to notify the fault condition to the rest of the system |

| bus_sys_rst_n     | input        | performs a global reset of the board                                                                                                                                                                                                               |

| bus_dsp_rst_n     | output       | generates a global reset to all DSP and HVC boards (can be SW generated internally by SW)                                                                                                                                                          |

| bus_fpga_clr_n    | input        | performs a soft reset of the board logic                                                                                                                                                                                                           |

| bus_driver_enable | Input/output | Used in HVC board to force unconditional disabling of high voltage drives (emergency situation). The signal can be monitored by the BCU and forced to disable drives under software control.                                                       |

| bus_boot_select   | input        | selects the default or user main logic configuration and on-chip program code at the board booting                                                                                                                                                 |

| bus_slot_id[0 3]  | input        | three static bits and one "three state" bit to identify the slot position from 0 to 31 where the control board is inserted                                                                                                                         |

Table 3 – Direct backplane bus signals

## 6.1.1.1.16 High speed communication description

The high speed communication is used to transfer the real time data between different parts of the MGAOS. The typical communication paths are shown on Figure 4.

Doc. : NGWFC\_RTC\_ASB\_002.doc lssue : 2 – March 28<sup>th</sup> , 2011

Page: 30 of 211

Figure 4 – High speed communication paths

Doc.: NGWFC\_RTC\_ASB\_002.doc Issue: 2 – March 28<sup>th</sup>, 2011

Page: 31 of 211

Data can be sent or to received from the high speed communication inputs or exchanged among DSPs. In the system logic, data packets are processed and, according to the message destination, are dispatched to the final receiver. This might be the local DSP, other DSPs within the same crate, another receiver on a different BCU board (not in the current application) or an external device (in our application, the TRS HBA. In this implementation data are read from BCU SDRAM).

The communication from/to the high speed interface modules goes through independent busses (10 bit wide, separated reception and transmission).

When data are sent to or received from the local DSP, the synchronous communication mode on the 64 bit parallel bus of the DSP is used. Data are transferred through a DMA channel on the DSP, therefore the data flow does not interfere with the DSP processing activity. Latencies can occur only if another DMA process attempts to access simultaneously to the same memory location in the DSP internal memory, which is an extremely rare condition. It is important to notice that the DSP parallel bus is used only for real time communication (this is true also for the DSP and HVC control boards).

If the data are destined to other DSPs on the same crate, the logic transfers the data through the 32bit bus on the backplane. Similarly as above, also this bus is dedicated only to real time data transfer.

The communication speed on both the DSP parallel bus and on the 32bit backplane bus is of 4Gbit/s.

#### 6.1.1.1.17 Diagnostic communication description

Diagnostic communication is destined to transfer commands and large amounts of diagnostic data with less stringent speed requirements. Diagnostic communication passes through the Ethernet port, which is connected by a dedicated PCI bus (32 bit) to the on-chip diagnostic processor in the system logic.

Diagnostic data might be transferred from/to the local DSP. To this aim, a dedicated interface, based on the DSP high speed synchronous communication ports (LinkPort) has been foreseen. The transfer rate is up to 2Gbit per second. This link does not interfere with the DSP bus activity, that supports the high speed communication, and can be also handled by DMA processes.

When diagnostic data need to be transferred to other DSPs on the same crate, a dedicated 16bit parallel bus is available on the backplane. This bus is similar to the high speed communication one (but 16bit wide), and has a throughput of 2Gbit per second.

Doc. : NGWFC\_RTC\_ASB\_002.doc lssue : 2 – March 28<sup>th</sup> , 2011

Page: 32 of 211

Figure 5 – Diagnostic communication paths

Doc.: NGWFC\_RTC\_ASB\_002.doc Issue: 2 – March 28<sup>th</sup>, 2011

Page: 33 of 211

#### 6.1.1.1.18 Boards layout

The BCU board PCB size is 196x91 mm. The limited available space forced to select components with very small SMD packages. Most of the components are mounted on the upper side of the board. The use of the bottom side is limited to decoupling capacitors and some analog components.

The components placing has been structured in functional zones. With reference to Figure 6, we can distinguish the following areas:

- Logic and computation: DSPs, FPGA, memories, configuration logic

- link communication front-end;

- Bus interface: B-LVDS drivers;

- Power supply: on-board switching and linear regulators;

Doc. : NGWFC\_RTC\_ASB\_002.doc lssue : 2 – March 28<sup>th</sup> , 2011

Page: 34 of 211

Figure 6 – BCU board components placing, with evidence of the different functional zones.

Doc. : NGWFC\_RTC\_ASB\_002.doc Issue : 2 – March 28<sup>th</sup> , 2011

Page: 35 of 211

Figure 7 – BCU board.

#### 6.1.1.2 AdOpt DSP BOARD

The *DSP board* is a very important component within the MGAOS. It performs the most heavy real time computations, namely residual wavefront computation and the control law servo computation. The total computational load is distributed in a parallel way among the 3 DSP boards foreseen within the system.

In other adaptive optics applications, the DSP board is directly interfaced to analog actuators and sensors. The analog section of the DSP board is not mounted on the boards dedicated to real-time computation only.

As an exception, the analog part is used for the DSP board that is part of the HVC board, as described in §6.1.1.3.

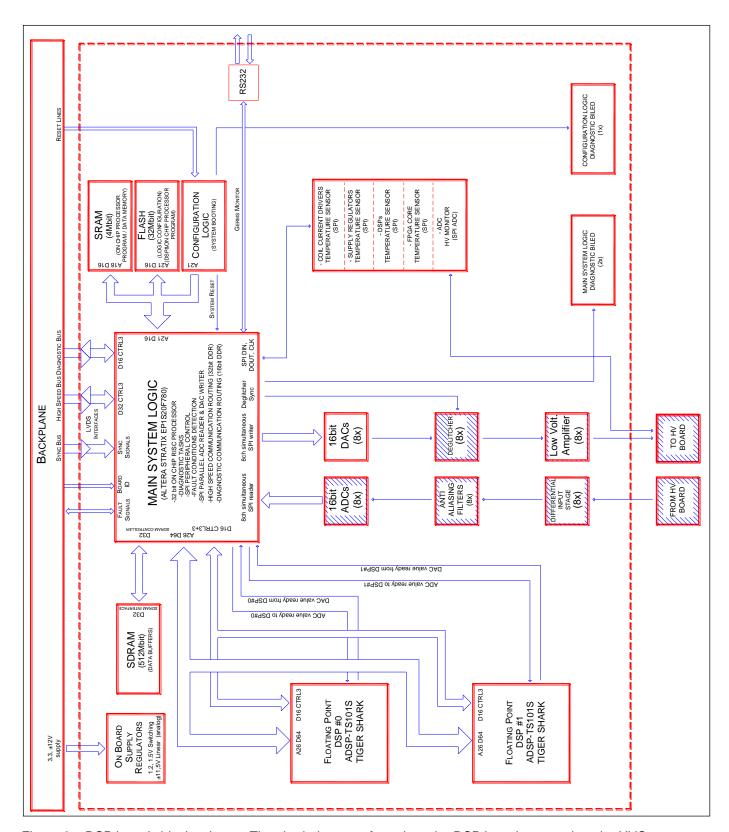

#### 6.1.1.2.1 DSP board block scheme

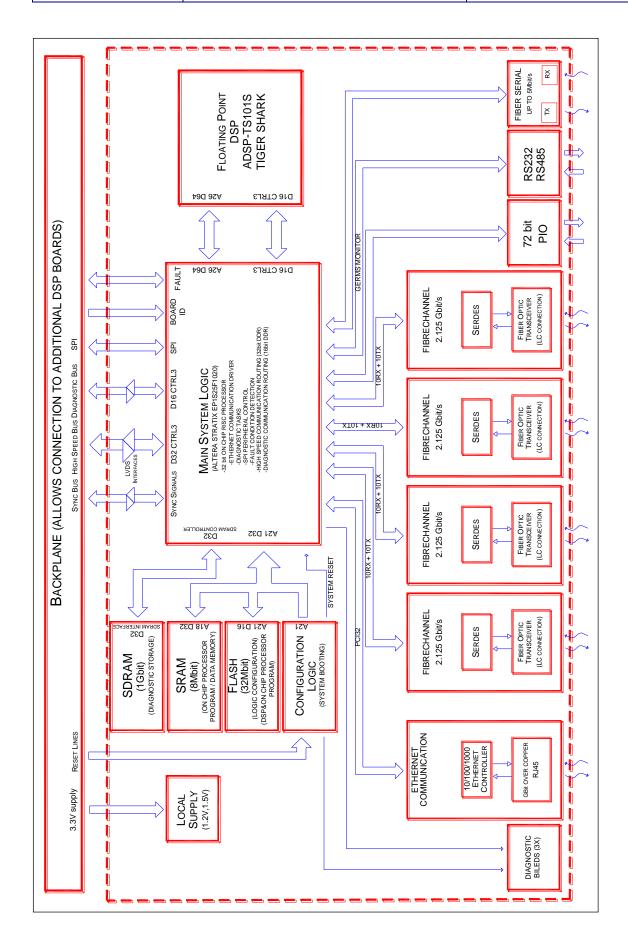

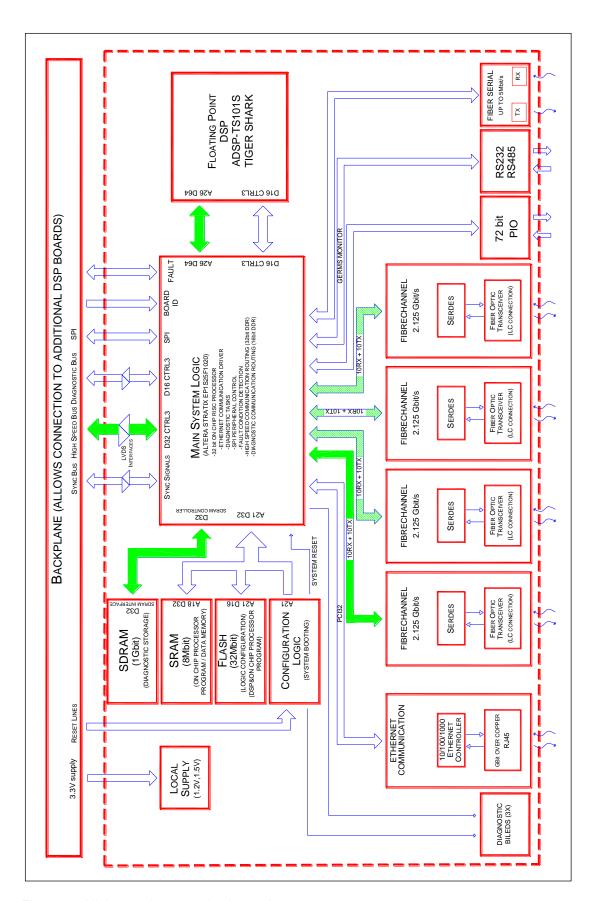

The block scheme of the DSP boards is presented in Figure 8.

Doc.: NGWFC\_RTC\_ASB\_002.doc Issue: 2 – March 28<sup>th</sup>, 2011

Page: 36 of 211

Figure 8 – DSP boards block scheme. The shaded parts refer only to the DSP board mounted on the HVC board.

Doc.: NGWFC\_RTC\_ASB\_002.doc Issue: 2 – March 28<sup>th</sup>, 2011

Page: 37 of 211

As shown in Figure 8 the DSP board architecture is designed around the Main System Logic. All data transfers within the board pass through the main system logic which creates the correct interface between the devices.

### 6.1.1.2.2 Main System Logic

The Main System Logic is realized with an Altera Startix EP1S20F780 programmable logic. It performs the following main tasks:

- the interface between all the on board devices;

- the interface with the backplane buses;

- the on chip processor, which performs the acquisition of all local diagnostic devices, the first level fault analysis and, if necessary, takes the actions correlated;

### 6.1.1.2.3 Computational devices

The computational part is realized with two ADSP-TS101S DSPs, where all real-time processing is performed.

The DSPs communicate with the main logic by two shared buses and some direct lines:

- the high speed bus has 64 data bits at 60MHz of frequency with a typical throughput of 4Gbit per second; The bus is shared among the two DSPs and the main system logic.

- the diagnostic bus uses two 8 data bits parallel serial lines (called link ports) in DDR mode at 60MHz of frequency, with a typical throughput of 2Gbit per second;

- dedicated hardware flags, directly connected between DSPs and main logic, to provide a proper synchronization and detection of completion of the computational steps

### 6.1.1.2.4 Configuration Logic

The configuration logic has identical function as in the BCU board. Refer to §6.1.1.1.3.

#### 6.1.1.2.5 Non volatile storage memory (FLASH)

The configuration logic has identical function as in the BCU board. Refer to §6.1.1.1.4.

In the HVC board, the FLASH memory contains also the calibration parameters (offset and gain) for each analog input/output channel.

### 6.1.1.2.6 SRAM memory

The 4Mbit SRAM memory is dedicated only to the main logic on-chip program and data memory. The organization of the memory depends to the on-chip program code.

The connection between the main logic and the SRAM is realized by a 16bit data bus at 60 MHz of frequency with a typical throughput of 1Gbit per second. This bus is shared with the FLASH device because during ordinary operation the FLASH is never used and then the bus is free to be used with the SRAM.

Doc. : NGWFC\_RTC\_ASB\_002.doc Issue : 2 – March 28<sup>th</sup> , 2011

Page: 38 of 211

#### 6.1.1.2.7 SDRAM memory

The 512Mbit SDRAM is used to storage real time data for diagnostic purposes. The main logic manages the bi-directional transfer of diagnostic data between SDRAM and DSPs' memory. Transfer from/to DSPs' memory is performed using a true DMA channel, therefore there is no software overhead by the DSP.

The data flow from the DSPs to the SDRAM is routed through the diagnostic channel, i.e. 16 bit 60MHz DDR LinkPort on DSP and 32 bit, 60MHz synchronous bus on SDRAM. The typical throughput is 2Gbit per second.

### 6.1.1.2.8 High speed backplane bus

The same considerations as in §6.1.1.1.7 apply to the high speed bus interface with the backplane. The DSP board is slave in the high speed communication. Internally, real time data are routed directly to/from both DSPs using the 64 bit DSP bus. Data transfers are handled by logic only and DSP memory is accessed in DMA, without requiring any software overhead. The high speed backplane bus is a 32bit data bus at 60MHz in DDR mode with a typical throughput of 4Gbit per second.

### 6.1.1.2.9 Diagnostic backplane bus

The same considerations as in §6.1.1.1.8 apply to the diagnostic bus interface with the backplane.

#### 6.1.1.2.10 The diagnostic serial monitor

A standard RS232 serial link allows to control and check the main logic functionalities and on-chip program flow during software development. This link is not available to the user and it is not foreseen to use it for ordinary operation of the board.

Doc. : NGWFC\_RTC\_ASB\_002.doc Issue : 2 – March 28<sup>th</sup> , 2011

Page: 39 of 211

#### 6.1.1.2.11 Direct backplane bus signals

From the backplane bus there are some directs signals which controls some hardware configurations or time critical events. The following table summarize these signals:

| Name              | Direction | Description                                                                                                                                                                                                                                        |  |

|-------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bus_power_fault   | in/out    | typically configured as an input to verify if an external power fault condition happens. If a fault condition happens inside the board the signal is driven as an output by the main logic to notify the fault condition to the rest of the system |  |

| bus_sys_rst_n     | input     | performs a global reset of the board                                                                                                                                                                                                               |  |

| bus_dsp_rst_n     | input     | performs a global reset of the board, similar to the bus_sys_rst_n from the control board point of view                                                                                                                                            |  |

| bus_fpga_clr_n    | input     | performs a soft reset of the board                                                                                                                                                                                                                 |  |

| bus_boot_select   | input     | selects the default or user main logic configuration and on-chip program code at the board booting                                                                                                                                                 |  |

| bus_driver_enable | input     | Used in HVC board to force unconditional disabling of high voltage drive (emergency situation)                                                                                                                                                     |  |

| bus_slot_id[0 3]  | input     | Three static bits and one "three state" bit to identify the slot position from to 31 where the control board is inserted                                                                                                                           |  |

Table 4 – Direct backplane bus signals

#### 6.1.1.2.12 Power supply

The DSP board requires a single 3.3V @ 1.5A typ. Other voltages are required for board operation, in particular 1.2V and 1.5V at relatively high currents for the DSP and FPGA cores respectively. The high accuracy, low impedance requirements on these power rails can be more easily satisfied if a distributed supply concept is adopted, where these low voltages are generated on-board by means of high efficiency, fast switching DC-DC converters.

The internal supply distribution scheme is resumed in Table 5.

| Supply of:   | Voltage | Current    | Generated by:                                         |

|--------------|---------|------------|-------------------------------------------------------|

| DSP core     | 1.2V    | 1.2*2=2.4A | On-board switching DC-DC converter, derived from 3.3V |

| FPGA core    | 1.5V    | 0.6A       | On-board switching DC-DC converter, derived from 3.3V |

| Logic, BLVDS | 3.3V    | 0.65A      | 3.3V (VCC)                                            |

Table 5 – DSP board supply distribution

Doc. : NGWFC\_RTC\_ASB\_002.doc Issue : 2 – March 28<sup>th</sup> , 2011

Page: 40 of 211

### 6.1.1.2.13 Mechanical configuration

The DSP board PCB size is 196x91 mm. The limited available space forced to select components with very small SMD packages. Most of the components are mounted on the upper side of the board. The use of the bottom side is limited to decoupling capacitors and some analog components.

The components placing has been structured in functional zones. With reference to Figure 9, we can distinguish the following areas:

- Logic and computation: DSPs, FPGA, memories, configuration logic

- Analog input: capacitive sensors input amplifier and ADCs (HVC board only)

- Analog output: DACs and low voltage amplifiers (HVC board only)

- Bus interface: B-LVDS drivers

- Power supply: on-board switching and linear regulators

The adopted scheme allowed to obtain a very efficient routing, in order to limit cross-talk problems.

Doc.: NGWFC\_RTC\_ASB\_002.doc Issue: 2 – March 28<sup>th</sup>, 2011

Page: 41 of 211

Figure 9 – DSP board components placing, with evidence of the different functional zones.

Doc.: NGWFC\_RTC\_ASB\_002.doc Issue: 2 – March 28<sup>th</sup>, 2011

Page: 42 of 211

Figure 10 – DSP board V3.0. The board in this picture is completely mounted, including the analog parts used only on the HVC board.

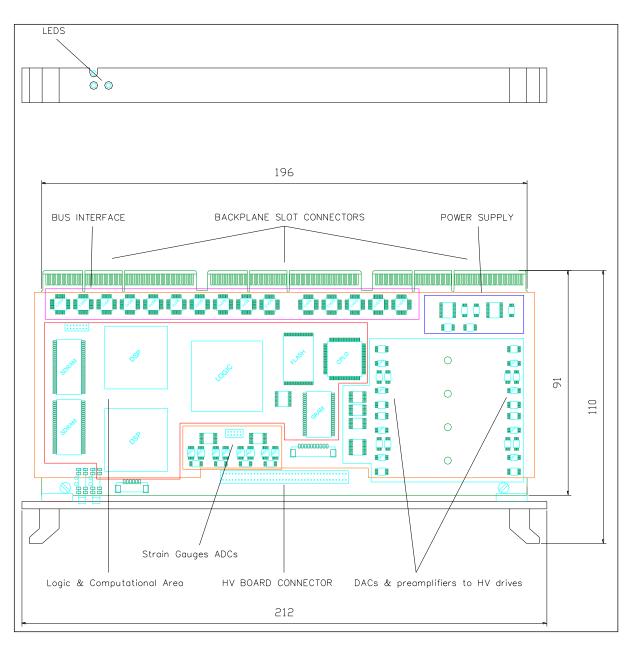

## 6.1.1.3 AdOpt HVC board

The purpose of the HVC board is to drive and control in open and closed loop the Tip-Tilt mirror units (DTT and UTT).

Within the HVC board, we can distinguish two main subsystems:

- digital and low voltage analog control board. This part is based on the AdOpt DSP board (see §6.1.1.2), with very little modifications, mainly change of some components value. This board has been specifically developed for controlling voice coil motor force actuators with a capacitive sensor position feedback. This design is very well consolidated and similar boards have been already manufactured in significant quantities.

- *High voltage analog drives and strain gauges conditioning circuitry*, placed on a second board directly interfaced (as daughter-board) to the AdOpt DSP board.

Doc. : NGWFC\_RTC\_ASB\_002.doc Issue : 2 – March 28<sup>th</sup> , 2011

Page: 43 of 211

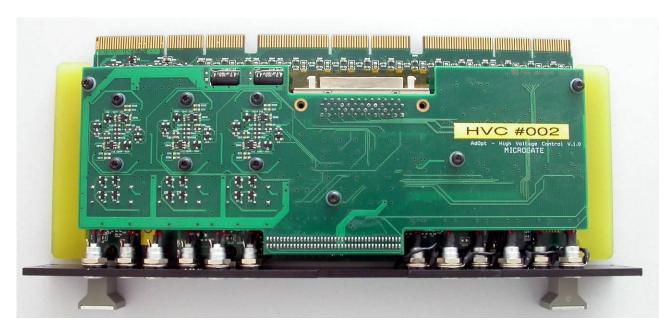

Figure 11 - HVC driver board

Figure 12 - HVC "mother" board

The AdOpt HVC board has 6 independent channels.