# NGAO Real Time Controller Design Document

| Revision History |                              |                |                                                           |  |  |

|------------------|------------------------------|----------------|-----------------------------------------------------------|--|--|

| Version          | Author                       | Date           | Details                                                   |  |  |

| 1.1              | Marc Reinig and Donald Gavel | May 8, 2009    | First draft version. Derived from MR's draft version 4.17 |  |  |

| Ver.2.2.37       | Marc Reinig and Donald Gavel | Dec 1, 2009    | Updated Draft                                             |  |  |

| Ver. 3.1.14      | Marc Reinig and Donald Gavel | April 28, 2010 | Updated Draft                                             |  |  |

# **Table of Contents**

| 1.  | Introdu | ction and Organization                                  | 1  |

|-----|---------|---------------------------------------------------------|----|

|     | 1.1 Rel | ationship to the Functional Requirements Document (FRD) | 1  |

|     | 1.2 Bac | ckground and Context                                    | 1  |

|     | 1.3 De: | sign Philosophy                                         | 3  |

|     | 1.4 Fur | nctions of the RTC System (FR-1401)                     | 3  |

|     | 1.5 Alg | orithm                                                  | 4  |

|     | 1.5.1   | Wavefront Reconstruction Algorithm                      | 4  |

|     | 1.5.2   | Inverse Tomography                                      | 5  |

|     | 1.5.3   | Massive Parallelization                                 |    |

|     | 1.6 Fur | nctional Architecture                                   |    |

|     | 1.6.1   | Control Processor (CP)                                  |    |

|     | 1.6.2   | Wave Front Sensors (WFS)                                | 9  |

|     | 1.6.3   | Tomography Engine                                       | 11 |

|     | 1.6.4   | DM Command Generators                                   | 12 |

|     | 1.6.5   | Disk Sub-System                                         |    |

|     | 1.6.6   | Global RTC System Timing                                |    |

|     | 1.6.7   | Diagnostics and Telemetry Stream                        |    |

|     |         | ysical Architecture                                     |    |

|     | 1.8 lm  | plementation Alternatives                               |    |

|     | 1.8.1   | Multi-core CPUs                                         |    |

|     | 1.8.2   | FPGAs                                                   |    |

|     | 1.8.3   | GPUs                                                    |    |

|     | 1.8.4   | Recommended implementations                             | 16 |

| 2.  | System  | Characteristics                                         | 18 |

|     | •       | sumptions and Performance Requirements                  |    |

|     |         | C States Visible to the AO Control                      |    |

|     |         | ning and Control of Internal States of the RTC          |    |

|     |         | liability and Recoverability                            |    |

|     | 2.3.1   | SEUs                                                    |    |

|     | _       |                                                         |    |

| 3.  |         | udgets, Latency, and Data Rates                         |    |

|     | 3.1 Err | or Budgets                                              |    |

|     | 3.1.1   | Accuracy                                                |    |

|     | 3.2 Lat | ency Summary                                            |    |

|     | 3.2.1   | Architectural Issues Affecting Latency                  |    |

|     | 3.2.2   | Latency Calculations for NGAO                           |    |

|     | 3.2.3   | Calculating Error Values Due to Latency                 |    |

|     | 3.3 Dat | ta Rates                                                | 36 |

| 4.  | RTC Co  | ntrol Processor (CP)                                    | 37 |

| 7.  |         | chitecture and Design                                   |    |

|     |         | Control System Feature Support                          |    |

|     | 4.2.1   | Commands                                                |    |

|     | 4.2.2   | Monitoring                                              |    |

|     | 4.2.3   | Events                                                  |    |

|     | 4.2.4   | Alarms                                                  |    |

|     | 4.2.5   | Log Messages                                            |    |

|     | 4.2.6   | Configuration                                           |    |

|     | 4.2.7   | Archiving                                               |    |

|     | 4.2.8   | Diagnostic Data Stream                                  |    |

|     | 4.2.8   | Computational Load                                      |    |

| Ver | 3 1 14  | Computational Load                                      |    |

|    | 4.3 Int          | erfaces and Protocols                                                |    |

|----|------------------|----------------------------------------------------------------------|----|

|    | 4.3.1            | Interface between the CP and the AO Control                          | 39 |

|    | 4.3.2            | Interface between the CP and the rest of the RTC                     | 40 |

| 5. | Camera           | IS                                                                   | 41 |

|    |                  | WFS (Tomography and Point-and-Shoot)                                 |    |

|    | 5.1.1            | Interfaces and Protocols                                             |    |

|    | 5.1.2            | Data Flow, Rates and Latency                                         |    |

|    | _                | WFS (IR)                                                             |    |

|    | 5.2.1            | Interfaces and Protocols                                             |    |

|    | 5.2.2            | Data Flow, Rates and Latency                                         |    |

|    | 5.3 Ma           | ster Clock Generation for Camera Synchronization                     |    |

|    | 5.3.1            | Inter Camera Capture Jitter                                          |    |

|    | 5.4 Coi          | ntrol                                                                |    |

|    | 5.4.1            | Gain                                                                 | 42 |

|    | 5.4.2            | Frame rate                                                           | 42 |

|    | 5.4.3            | Frame Transfer Rate                                                  | 42 |

|    | 5.4.4            | Internal Camera Clock Speeds and Parameters                          |    |

| c  | Maya F           | ront Sensors (WFSs)                                                  | 44 |

| 6. |                  | S Mode                                                               |    |

|    |                  | orithms                                                              |    |

|    | 6.2.1            | Centroiding Algorithms                                               |    |

|    | 6.2.2            | Reconstruction and Tomography Algorithms                             |    |

|    |                  | S Interfaces                                                         |    |

|    |                  | ta Flow and Rates                                                    |    |

|    |                  | WFSs (Low Order Wave Front Sensors) (for T/T, Astigmatism and Focus) |    |

|    | 6.5.1            | Architecture and Design                                              |    |

|    | 6.5.2            | Interfaces and Protocols                                             |    |

|    | 6.5.3            | Data Flow, Rates and Latencies                                       |    |

|    | 6.5.4            | Low Order Command Generation                                         |    |

|    |                  | WFSs (High Order Wave Front Sensors)                                 |    |

|    | 6.6.1            | Centroider and Wave Front Reconstruction Engine                      |    |

|    | 6.6.2            | Tomography HOWFS                                                     |    |

|    | 6.6.3            | Point-and-Shoot HOWFS                                                |    |

|    |                  | S Wave Front Sensor                                                  |    |

| _  |                  |                                                                      |    |

| 7. |                  | mography Engine (TE)                                                 |    |

|    |                  | ocessing the Data                                                    |    |

|    |                  | chitecture                                                           |    |

|    | 7.2 Ma<br>7.2.1  | Inter Element Communications                                         |    |

|    |                  |                                                                      |    |

|    | 7.2.2<br>7.3 Pro | Layer-to-layer and Guide-Star-to-Guide-Star Communications           |    |

|    |                  | plementation                                                         |    |

|    | 7.4 1111         | General Operation                                                    |    |

|    | 7.4.1<br>7.4.2   | •                                                                    |    |

|    | 7.4.2<br>7.4.3   | The Systolic Array The processing element (PE)                       |    |

|    | 7.4.3<br>7.4.4   | PE interconnect                                                      |    |

|    | 7.4.4<br>7.4.5   | I/O bandwidth                                                        |    |

|    | 7.4.5<br>7.4.6   | SIMD System Control                                                  |    |

|    | 7.4.6<br>7.4.7   | Cycle Accurate Control Sequencer (CACS)                              |    |

|    | 7.4.7<br>7.4.8   | Timing and Events                                                    |    |

|    | 7.4.8<br>7.4.9   | Control and Orchestration of Processor States                        |    |

|    | , .4.5           | Control and Ordinestration of Frocessor States                       | /3 |

|     | 7.5 Design                                                                           | 73         |

|-----|--------------------------------------------------------------------------------------|------------|

|     | 7.5.1 Physical Architecture of the Tomography Engine                                 | 73         |

|     | 7.5.2 FPGA Design                                                                    | <b>7</b> 3 |

|     | 7.5.3 Board Design                                                                   | 74         |

|     | 7.5.4 System (Multi-Board)                                                           | 75         |

|     | 7.6 Other Architectural Issues                                                       | 75         |

|     | 7.6.1 Program Flow Control                                                           | 75         |

|     | 7.6.2 Arithmetic Errors and Precision                                                | 76         |

| 8.  | DM and T/T Command Generation                                                        | 77         |

|     | 8.1 Algorithms                                                                       |            |

|     | 8.2 Tip/Tilt Mirrors                                                                 |            |

|     | 8.2.1 Tip/Tilt Command Generators                                                    |            |

|     | 8.2.2 Systematic Vibration Compensation (FR-XXXX, no current functional requirement) |            |

|     | 8.2.3 Interfaces and Protocols                                                       |            |

|     | 8.2.4 Data Flow and Rates                                                            |            |

|     | 8.3 DM Command Generators                                                            |            |

|     | 8.3.1 Low Order (Woofer) (On-axis DM, closed loop operation)                         |            |

|     | 8.3.2 High Order (Tweeter) (Science and LOWFS DMs, Open Loop Operation)              |            |

| _   |                                                                                      |            |

| 9.  | NGS Mode Operation                                                                   | 83         |

| 10. | Telemetry, Diagnostics, Display and Offload Processing                               | 84         |

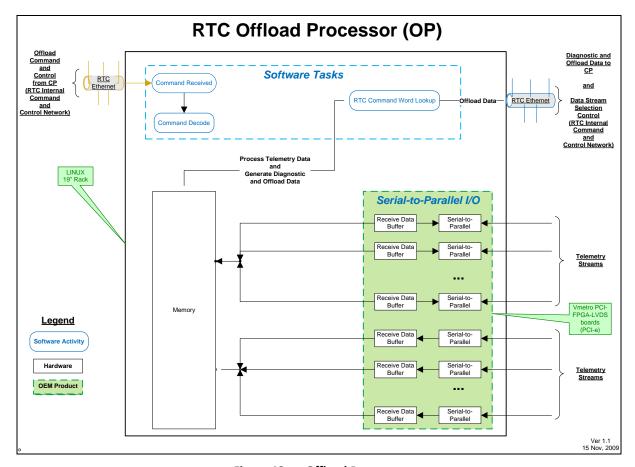

|     | 10.1 Architecture and Design                                                         | 85         |

|     | 10.1.1 Offload Processor (OP)                                                        | 85         |

|     | 10.2 Interfaces and Protocols                                                        | 86         |

|     | 10.3 Data Flow and Rates                                                             | 86         |

|     | 10.4 Synchronization of AO Data Time Stamps with the Science Image Time Stamps       | 87         |

|     | 10.5 An Important Note on the Telemetry Rates                                        | 87         |

|     | 10.6 Handling System Diagnostic Functions                                            | 88         |

| 11. | RTC Disk Sub-System                                                                  | 89         |

|     | 11.1 Interfaces and Protocols                                                        | 89         |

|     | 11.1.1 Interface to the RTC                                                          | 89         |

|     | 11.1.2 Interface to the System AO Control                                            | 89         |

|     | 11.2 Data Flow and Rates                                                             | 89         |

|     | 11.2.1 RTC Telemetry Port                                                            | 89         |

|     | 11.3 Storage Capacity                                                                | 89         |

| 12  | Timing Generation and Control                                                        | 90         |

|     | 12.1 Camera Synchronization and Timing                                               |            |

|     | 12.2 GPS Sub millisecond Time Stamp Source                                           |            |

|     | 12.3 Global Tomography Synchronization                                               |            |

|     | 12.3.1 Global Reset                                                                  |            |

|     | 12.3.2 Global Synch                                                                  |            |

|     | 12.3.3 System Clock                                                                  |            |

|     | 12.3.4 LVDS Clock (600 MHz)                                                          |            |

| 13. | RTC Physical Architecture                                                            | 91         |

| 14  | RTC Test Bench                                                                       | Q/         |

| _7. | 14.1 Interfaces and Protocols                                                        |            |

|     | 14.2 Data Flow and Rates                                                             |            |

|     | 14.3 Architecture                                                                    |            |

| 4-  |                                                                                      |            |

| 15. | Test Plan                                                                            | 96         |

|          |                      | uirements for System Components (HW and SW)                                      |     |

|----------|----------------------|----------------------------------------------------------------------------------|-----|

|          | •                    | onents                                                                           |     |

|          |                      | eptance Testing                                                                  |     |

|          |                      | g Term Maintenance Plan                                                          |     |

|          |                      | ument Control                                                                    |     |

|          |                      | dware                                                                            |     |

|          |                      | Components                                                                       |     |

|          |                      | umentation and Training<br>ware                                                  |     |

|          |                      | dwaredware                                                                       |     |

|          |                      |                                                                                  |     |

|          |                      | bution, Environment and Cooling                                                  |     |

|          |                      | quencing                                                                         |     |

|          |                      | A Power Dissipation                                                              |     |

|          |                      | nography Engine Coolingnand Generation                                           |     |

|          |                      | System                                                                           |     |

|          |                      | Processor (CP)                                                                   |     |

|          |                      | nent                                                                             |     |

|          |                      |                                                                                  |     |

|          |                      | rare and Software not Otherwise Covered                                          |     |

|          |                      | System State Information                                                         |     |

|          |                      | Networking                                                                       |     |

|          |                      | S                                                                                |     |

|          |                      | t Cables                                                                         |     |

| -        | •                    |                                                                                  |     |

|          | oendix A             | Glossary                                                                         |     |

|          | oendix B             | GPU RTC Benchmarking                                                             |     |

|          | oendix C             | Time-related keywords in Keck Observatory FITS files                             |     |

|          | oendix D             | WFS Detailed Timing Calculations                                                 |     |

|          | oendix E             | Tomography Engine Detailed Timing Calculations                                   |     |

|          | oendix F<br>oendix G | Itemized List of Cameras, T/T Mirrors, DMs, and Actuators                        |     |

|          | oendix H             | Real-Time Control Numerical Analysis                                             |     |

|          | oendix I             | Tomography Array Size and Cost Estimate                                          |     |

|          |                      |                                                                                  |     |

| 20. Re   | eferences .          |                                                                                  | 124 |

| •        |                      |                                                                                  |     |

|          |                      |                                                                                  |     |

| Table    | e of Figu            | ıres                                                                             |     |

| Figure 1 | _                    | d View of the RTC                                                                | 2   |

| Figure 2 | •                    | ont Reconstruction Algorithm for HOWFS and NGS                                   |     |

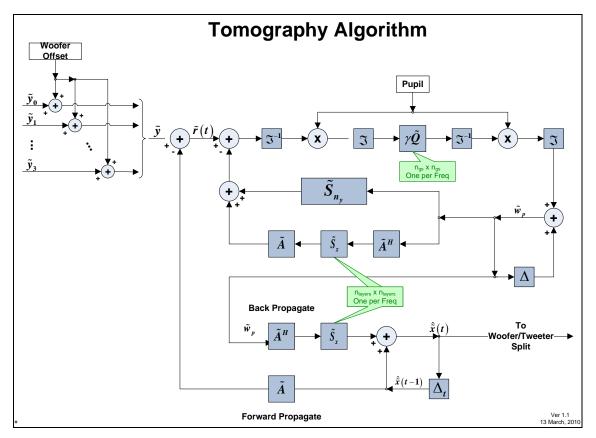

| Figure 3 |                      | phy Algorithm                                                                    |     |

| Figure 4 | _                    | I view of the AO Control's View of the RTC. See Figure 8 for a detailed view     |     |

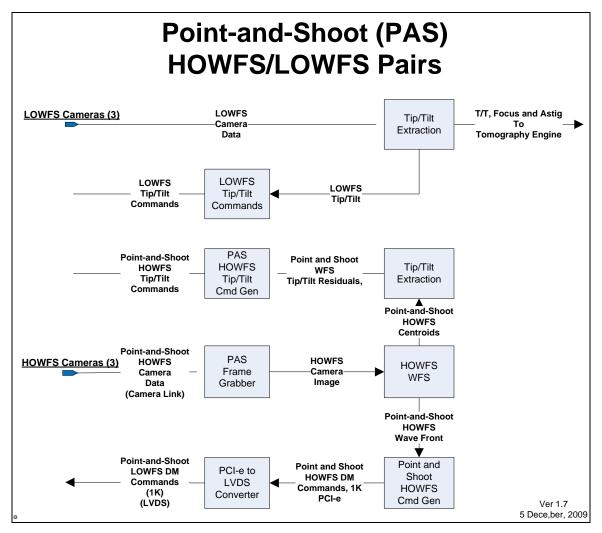

| Figure 5 | =                    | d-Shoot HOWFS/LOWFS Pair                                                         |     |

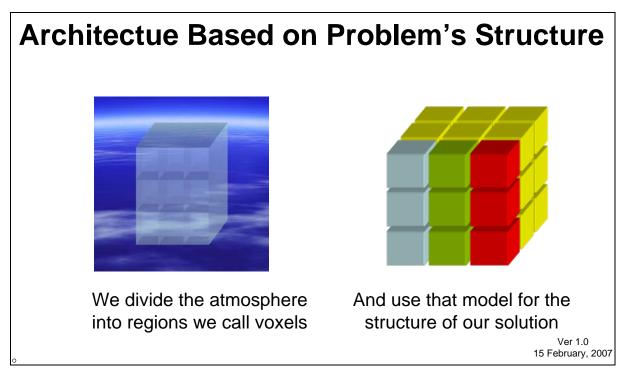

| Figure 6 |                      | ng Elements Mapping to the Atmospheric Model                                     |     |

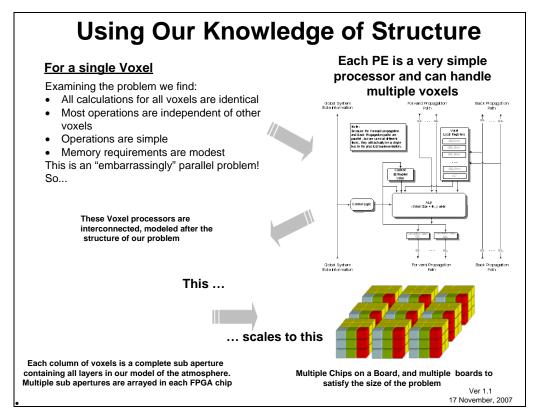

| Figure 7 |                      | Processing Elements to the Problem                                               |     |

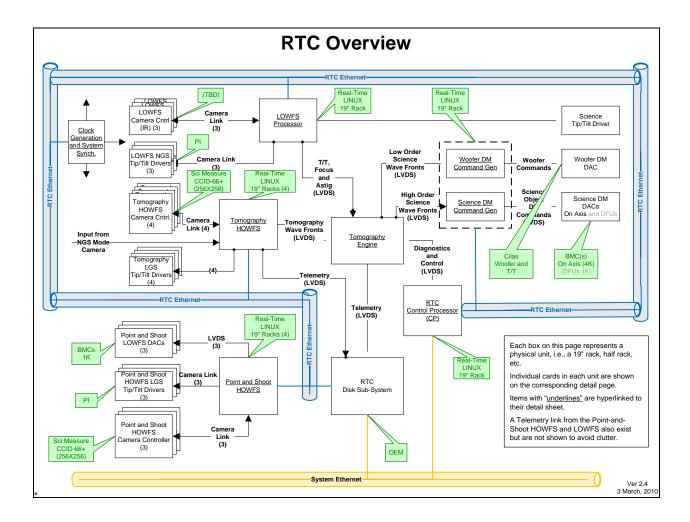

| Figure 8 |                      | v of the RTC sub-systems                                                         |     |

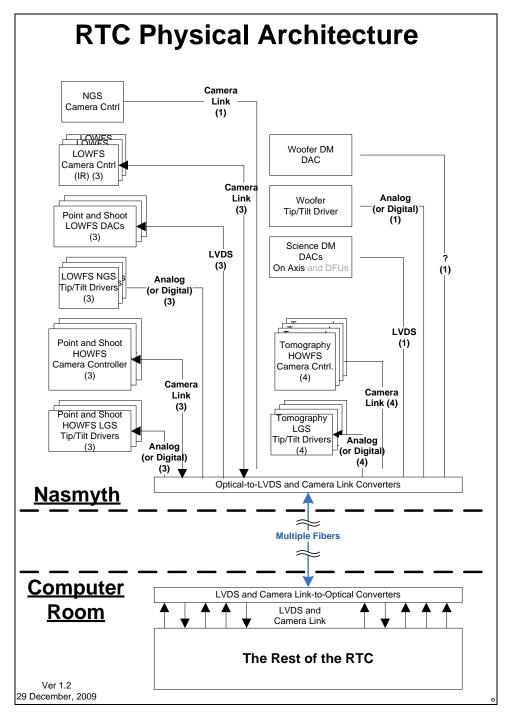

| Figure 9 | RTC Phys             | sical architecture, showing the divide between the Nasmyth and the computer room | 15  |

| Figure 1 |                      | Sub-System States Viewable by the AO Control                                     |     |

| Figure 1 | .1 Overall F         | RTC Latency Components (not to scale)                                            | 25  |

|          |                      |                                                                                  |     |

| Figure 12 | Non-Pipelined Latency (not to scale)                                               | 27  |

|-----------|------------------------------------------------------------------------------------|-----|

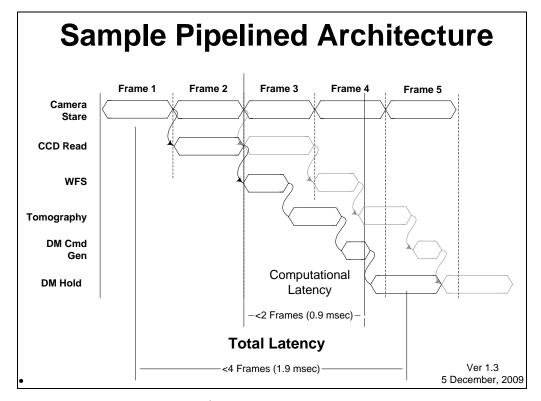

| Figure 13 | Pipelined Architecture Latency (not to scale)                                      | 28  |

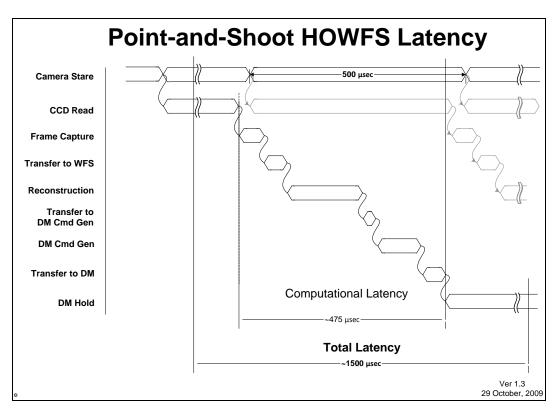

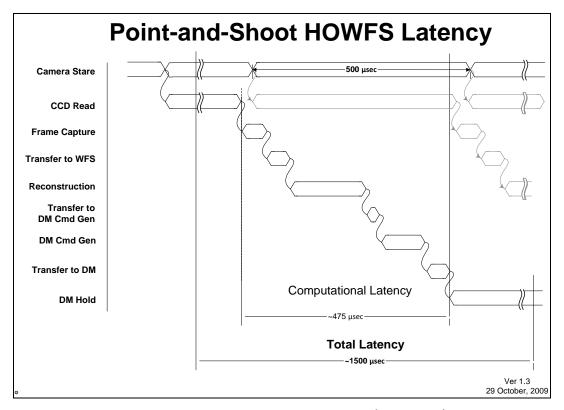

| Figure 14 | Point-and-Shoot HOWFS Latency                                                      | 30  |

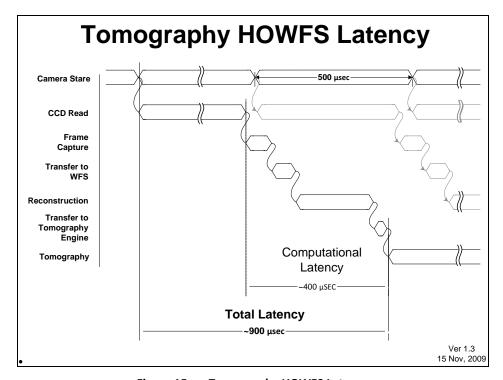

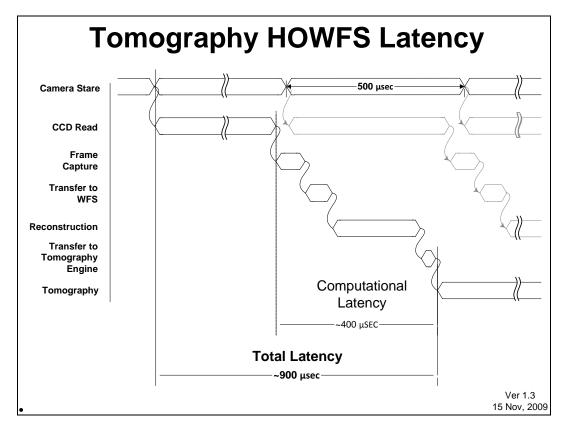

| Figure 15 | Tomography HOWFS Latency                                                           | 31  |

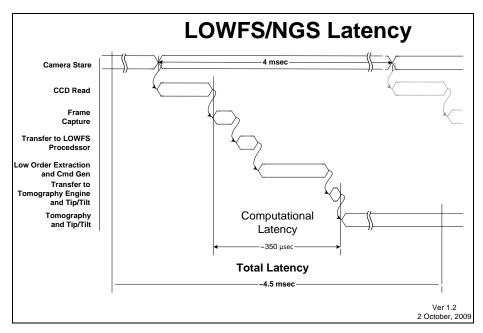

| Figure 16 | LOWFS/NGS Latency                                                                  | 32  |

| Figure 17 | RTC Latency                                                                        | 35  |

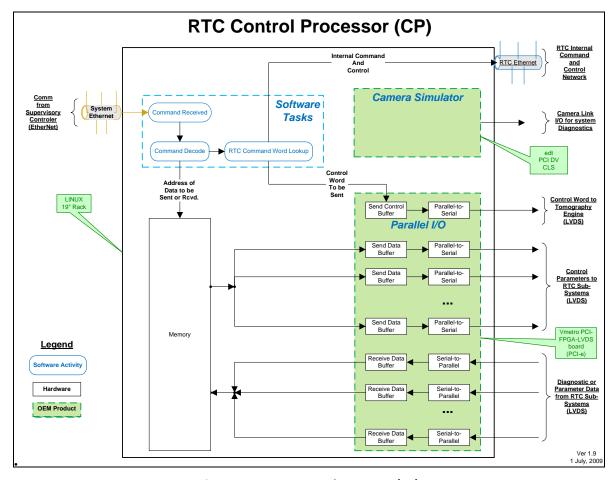

| Figure 18 | RTC Control Processor (CP)                                                         | 38  |

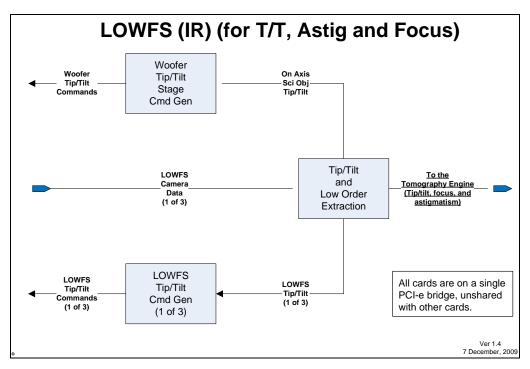

| Figure 19 | LOWFS                                                                              | 46  |

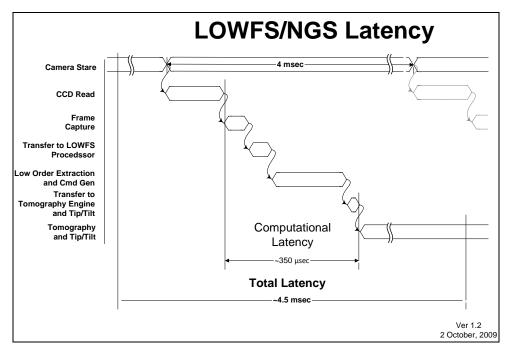

| Figure 20 | LOWFS Latency (not to scale)                                                       | 47  |

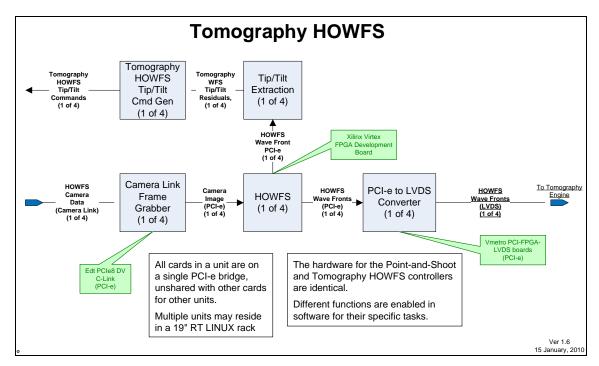

| Figure 21 | Tomography HOWFS                                                                   | 50  |

| Figure 22 | Tomography WFS Latency (not to scale)                                              | 50  |

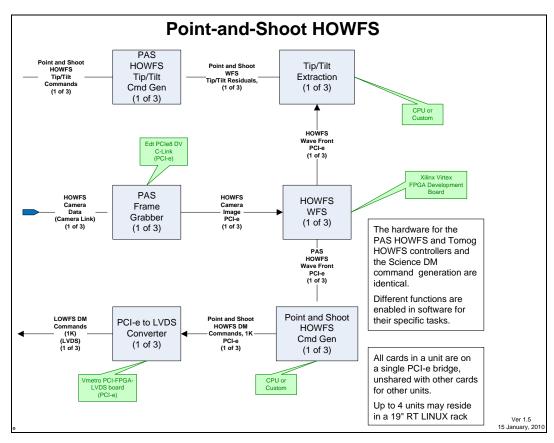

| Figure 23 | Point-and-Shoot HOWFS                                                              | 51  |

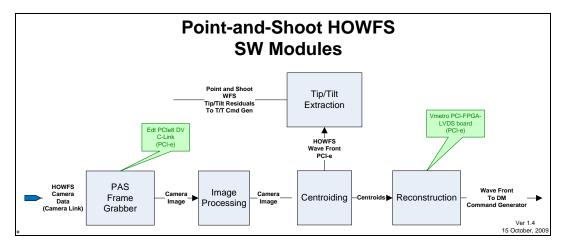

| Figure 24 | Point-and-Shoot HOWFS SW Modules                                                   | 52  |

| Figure 25 | Point-and-Shoot HOWFS Latency (not to scale)                                       | 52  |

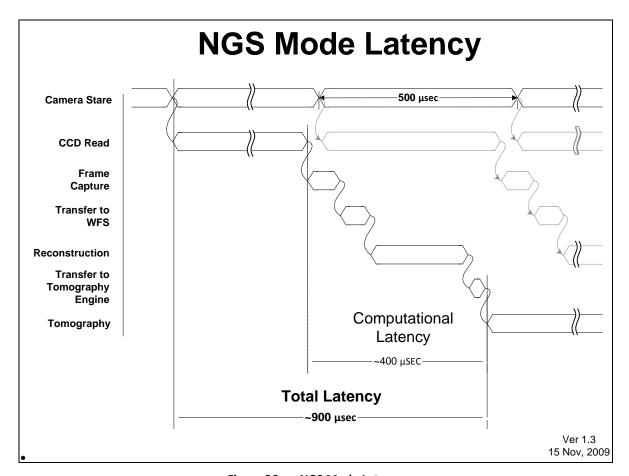

|           | NGS Mode Latency                                                                   |     |

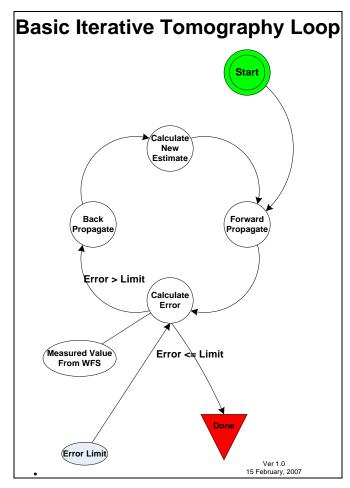

| Figure 27 | The basic iterative tomography algorithm                                           | 56  |

| Figure 28 | Actual Fourier Domain Data Flow with Aperturing                                    | 57  |

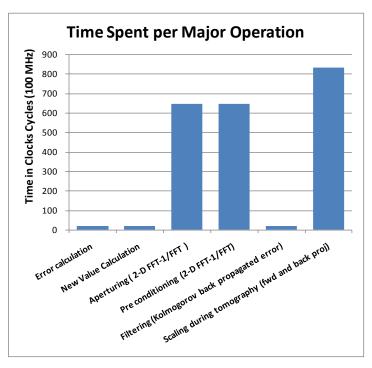

| Figure 29 | Relative time of components of iterative loop                                      | 58  |

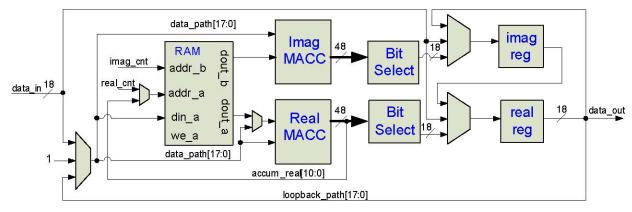

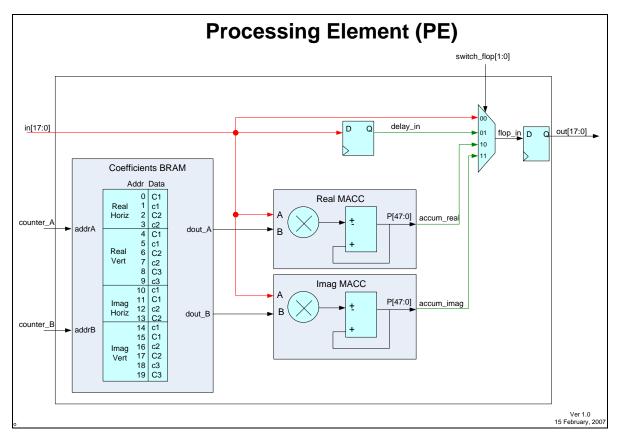

| Figure 30 | Processing Element (PE) diagram                                                    | 59  |

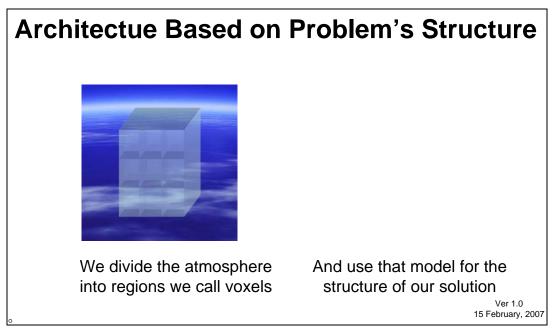

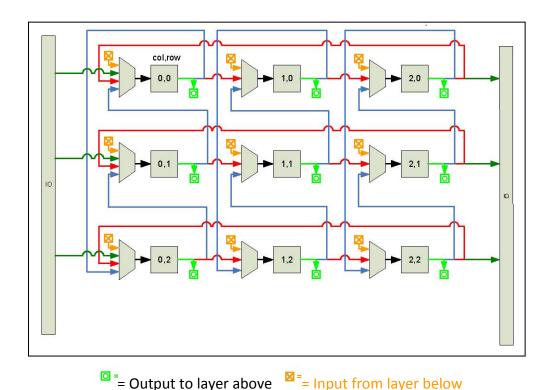

| Figure 31 | Modeling the solution after the form of the problem                                | 60  |

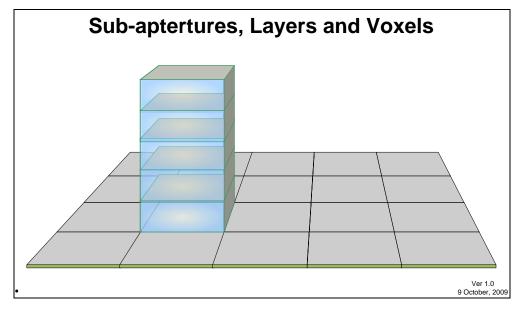

| Figure 32 | A column of combined layer and guide star processors form a sub aperture processor | 60  |

| Figure 33 | Using our knowledge of structure                                                   | 61  |

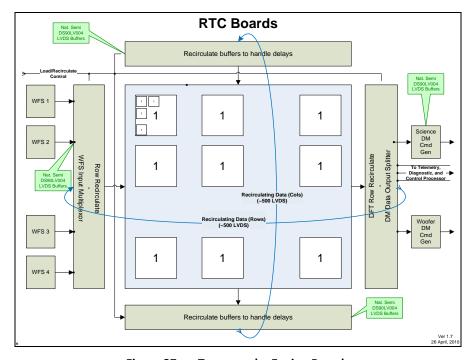

|           | Tomography Engine Block Diagram                                                    |     |

|           | The Systolic Array, showing boundaries for different elements                      |     |

|           | Extended Sub Aperture due to FOV                                                   |     |

| Figure 37 | Tomography Engine Boards                                                           | 67  |

| Figure 38 | Processing Element (PE)                                                            | 68  |

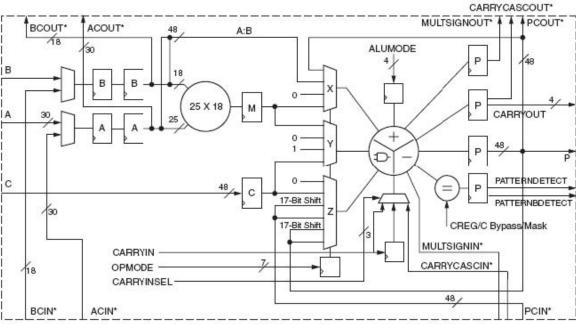

| Figure 39 | The Xilinx DSP48E architecture []                                                  | 69  |

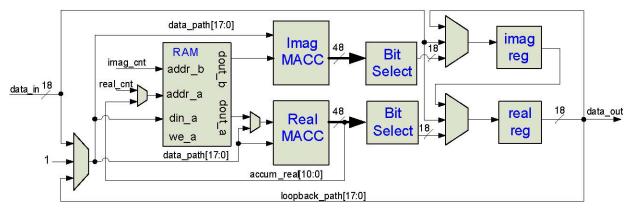

| _         | A single Processing Element (PE)                                                   |     |

| -         | A layer of PEs, showing the interconnect and I/O                                   |     |

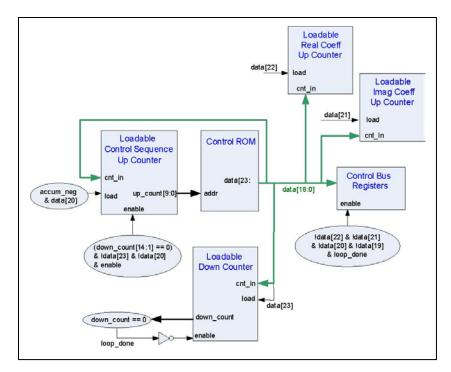

| -         | CACS Architecture                                                                  |     |

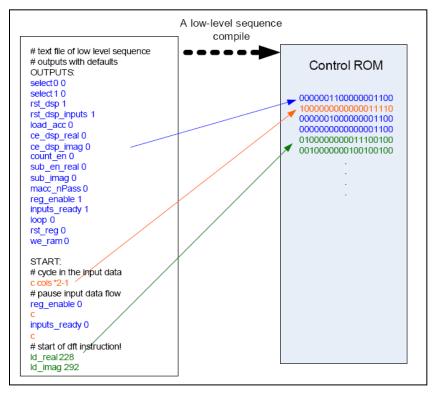

| _         | Sample CACS ROM content                                                            |     |

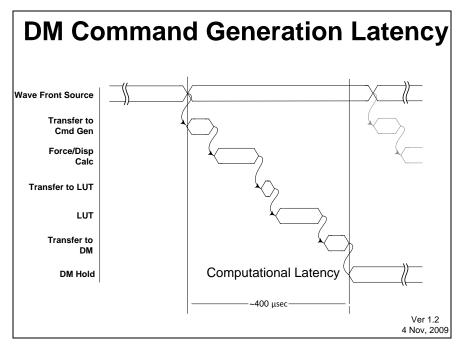

| _         | DM Command Generation Latency (not to scale)                                       |     |

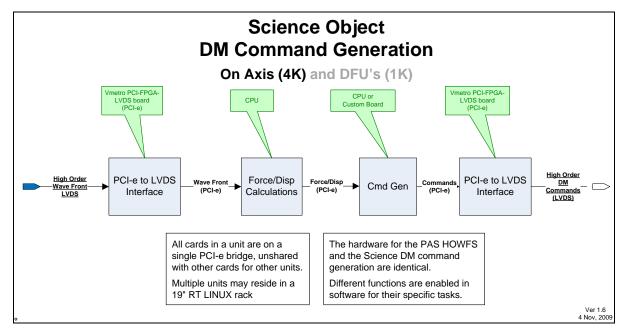

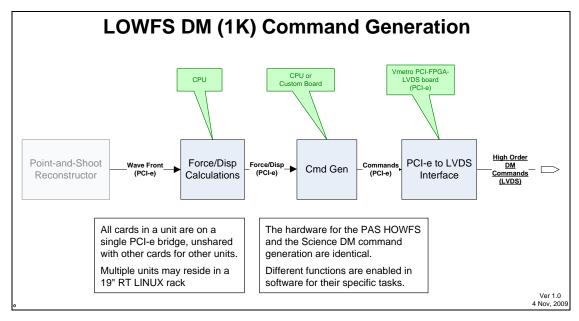

|           | Science Object DM command generation                                               |     |

| -         | LOWFS Command Generation                                                           |     |

| •         | RTC Diagnostics and Telemetry                                                      | 85  |

| -         | Offload Processor                                                                  | 86  |

| -         | Split of RTC hardware between the computer room and the Naismith                   |     |

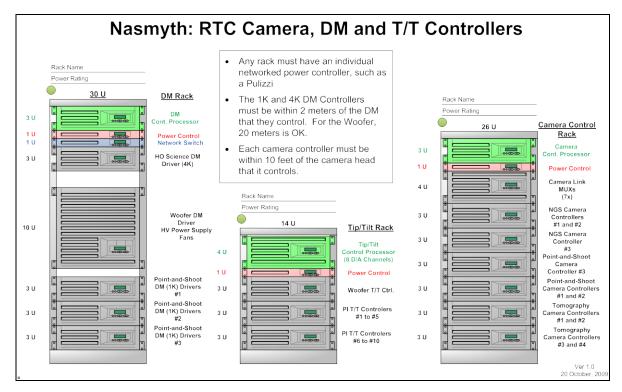

|           | Rack space required on the Nasmyth for the camera, DM and T/T controllers          |     |

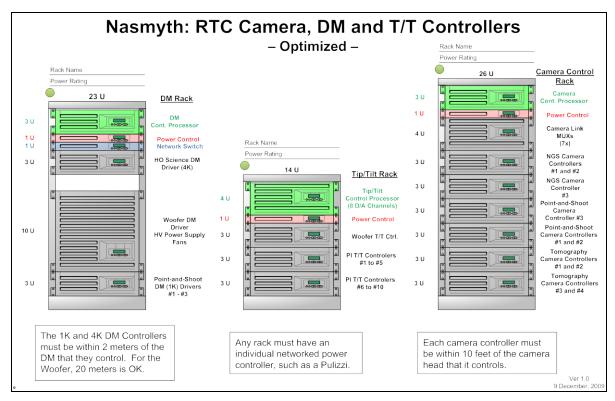

| •         | Possible optimization of rack space required on the Nasmyth                        |     |

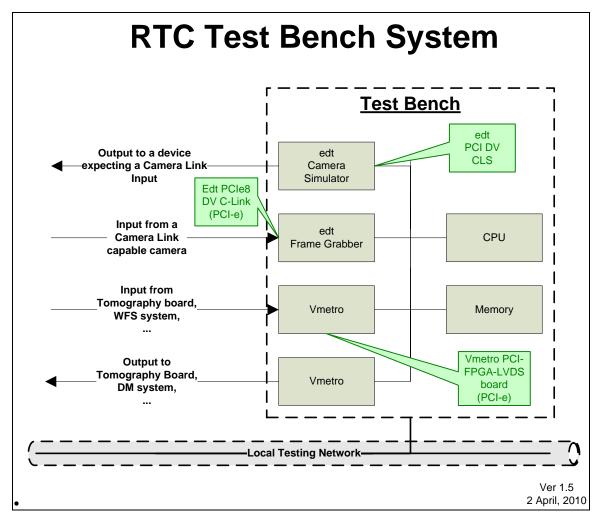

| -         | RTC Test Bench                                                                     |     |

| -         | Power Distribution                                                                 |     |

| -         | GPU Transfer Rates                                                                 |     |

| -         | PE Detailed Design                                                                 |     |

| -         | In-place DFT accumulation                                                          |     |

| _         | Gantt chart for pipelined DFT                                                      |     |

| Figure 58 | Example Verilog code for ALU                                                       | 117 |

| •         |                                                                                    |     |

# **Table of Tables**

| Table 1 | NGAO RTC System Assumptions | 18           |

|---------|-----------------------------|--------------|

|         |                             | - /4 - /2046 |

# **NGAO RTC Design Document**

| Table 2  | NGAO RTC Latency Summary                                                       | 22                |

|----------|--------------------------------------------------------------------------------|-------------------|

| Table 3  | NGAO RTC System Parameters (Note: the Point-and-Shoot WFS use 30 and 44 sub ap | ps. Instead of 60 |

| and 88)  | 30                                                                             |                   |

| Table 4  | Tomography Transfer Latencies and Rates                                        |                   |

| Table 5  | Point-and-Shoot HOWFS Transfer Latencies and Rates                             | 33                |

| Table 6  | NGS Mode Transfer Latencies and Rates                                          | 33                |

| Table 7  | LOWFS Data Rates and Latency Calculations                                      | 33                |

| Table 8  | Non-Transfer Latencies                                                         | 34                |

| Table 9  | Total Latency Calculations                                                     | 35                |

| Table 10 | Total NGS Latency Calculations                                                 | 35                |

| Table 11 | Data Rate Summary                                                              | 36                |

| Table 12 | Board Stack Up                                                                 | 74                |

| Table 13 | Major Telemetry and Data Transfer Rates                                        | 87                |

| Table 14 | Preliminary FPGA Power Dissipation Analysis                                    | 101               |

| Table 15 | Reconstruction Time Estimates for GPU                                          | 108               |

| Table 16 | Detailed WFS Timing Calculations                                               |                   |

| Table 17 | Detailed Tomography Timing Calculations                                        | 115               |

| Table 18 | List of sensors and actuators connected to the RTC                             | 118               |

| Table 19 | Estimate of the Tomography Engine Array Size and Cost                          | 123               |

|          |                                                                                |                   |

Ver. 3.1.14

# 1. Introduction and Organization

This document covers the preliminary design of the Keck  $\underline{N}$ ext  $\underline{G}$ eneration  $\underline{A}$ daptive  $\underline{O}$ ptics  $\underline{R}$ eal  $\underline{T}$ ime  $\underline{C}$ ontroller (NGAO RTC).

This section is an overall introduction and summary of the RTC architecture and concept for implementation. The section also describes the organization of the remainder of this document.

Section 2 describes the overall system characteristics.

Section 3 covers the latency and timing requirements that drive the architecture and implementation decisions.

Sections 4 through 12 cover the individual sub-systems in the RTC grand scope, including the Control Processor (CP), Wave Front Sensors (WFSs), Tomography Engine (TE), DM and Mirror Command Generators.

Subsequent sections are supplementary material covering broader RTC issues or related topics. For details on the algorithms, see [1].

# 1.1 Relationship to the Functional Requirements Document (FRD)

Each section of this document describes the design of the hardware or software that is intended to satisfy one or more of the functional requirements set forth in the RTC FRD (KAON 573, superseded by the entries in the Contour requirements database).

Where appropriate, an annotation, "FR-XXXXX", is noted throughout this document that refers to a specific functional requirement in the FRD that is being addressed.

# 1.2 Background and Context

The design of the Real-Time Processor for the Keck Next Generation Adaptive Optics system represents a radically new computational framework that blazes new territory for astronomical AO systems. The need for a new approach is due to the considerable step up in the amounts of data to be processed and controls to be driven in a multiple guide star tomography system. Furthermore, KNGAO has set ambitious new goals for wavefront correction performance that puts further pressure on processing rates and latency times that traditional compute paradigms have trouble scaling up to. Current processing requirements are in the Terra Operations per second region. Instead, the KNGAO RTC is structured around a massively parallel processing (MPP) concept, where the highly parallelizable aspects of the real-time tomography algorithm are directly mapped to a large number of hardware compute elements. These compute elements operate separately and simultaneously. With this approach, increasing problem size is handled roughly by increasing the number of processor elements, rather than processor speed.

In short, in this design, the structure of the algorithm drives the structure of the hardware. Therefore, it is necessary to understand the algorithm itself to understand the hardware

architecture, so please review the companion volume, see Gavel, D., NGAO Real Time Control Algorithms Document, KAON xxx, 2009, which presents the technical details of the massively parallel algorithm for AO tomography.

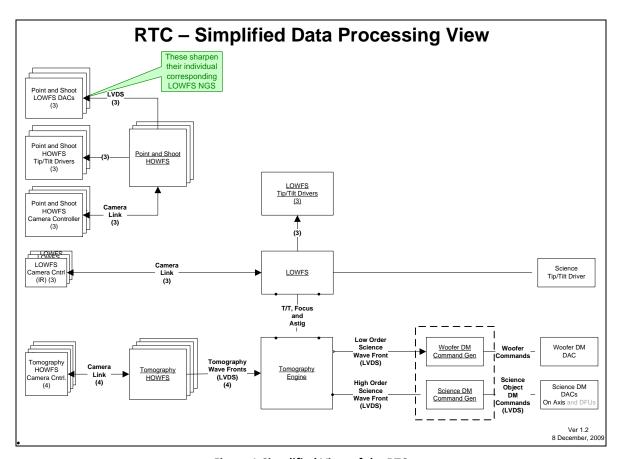

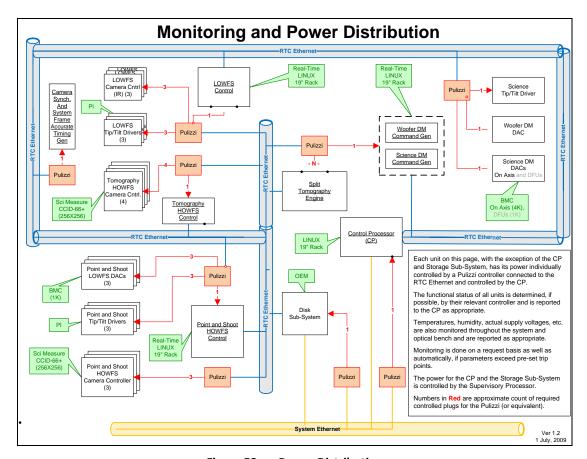

For the purpose of introducing the hardware design, the algorithm and hardware have three main top-level component steps: wavefront sensing, tomography, and DM control. These physically map to component blocks of hardware, see Figure 1. The actual physical layout of boards and connecting cables mimic this geometry. Inside the blocks, further parallelization is achieved by use of Fourier domain processing, where each spatial frequency component is processed independently. Fourier-domain algorithms have been developed in recent years for wavefront phase reconstruction [2] and for tomography [3].

Figure 1 Simplified View of the RTC

As stated, the real-time processing takes place on small compute elements, either Field-Programmable Gate Arrays (FPGAs, Graphical Processing Units (GPUs), or multiple processors and cores.

FPGA devices have been used in the digital electronics industry since the 1980's, when they were first used as alternatives to custom fabricated semiconductors. The arrays of raw unconnected logic were "field-programmed" to produce any digital logic function. They grew in

a role as support chips on board computer motherboards and plug-in cards. Recent versions incorporate millions of transistors and some also incorporate hundreds to thousands of on-chip conventional arithmetic processors. Their use is now common in many products from high performance scientific add in boards to consumer portable electronics including cell phones. Today these chips represent a fast growing, multi-billion dollar industry.

Graphical Processing Units were first introduced to offload the video processing for computer displays from the computer's CPU. They have since developed as a key processor for digital displays, which have demanding applications in computer-aided design and video gaming. GPUs specialize in geometric rotations, translations, and interpolation using massive vector-matrix manipulations. Beyond graphics, GPUs are also used in analyzing huge geophysical signal data sets in oil and mineral exploration and other scientific calculations requiring extremely high performance. It is possible that GPUs can be adapted to the wavefront reconstruction problem through these means and, while they remain a possible low-cost option for the front-end video processing, our baseline design uses FPGA processors for this purpose.

The RTC uses a mix of CPUs, GPUs, and FPGAs to best match their individual strengths to the RTC's needs.

# 1.3 **Design Philosophy**

For efficiency, we are maximizing the use of existing designs and code. The WFS and the DM drivers are based on the heritage of the Villages and GPI adaptive optics systems for wavefront reconstruction and open loop DM control.

To insure the maximum reliability, serviceability, and maintainability, we have maximized the use of commodity parts and industry standard interfaces.

# 1.4 Functions of the RTC System (FR-1401)

- 1. Measure the atmosphere using 7 laser guide stars (3 point-and-shoot and 4 tomography) and 3 natural guide stars, producing, respectively, high-order wave fronts and low-order wavefronts (tip/tilt, focus, and astigmatism values) based on these measurements. The 3 point-and-shoot guide stars are used only to sharpen the natural guide stars used for T/T, focus and astigmatism). The 4 tomography lasers are used to probe the atmosphere for the tomography engine.

- 2. Using the measurements from the four tomography WFS, estimate the three dimensional volume of atmospheric turbulence-induced index-of-refraction variations over the telescope (tomographic reconstruction).

- 3. The point-and-shoot high order wave front sensors (HOWFS) determine the shapes of the multiple deformable mirrors' (DMs) surfaces that will correct for the turbulence along paths to their natural guide stars at their correspondingly assigned positions on the sky. All WFS provide T/T information for its own tip/tilt mirror.

- 4. Using the desired surface shape, generate the correct voltage commands for each DM and tip/tilt mirror actuator, compensating for any non linearity or influence functions.

- 5. Capture any diagnostic and telemetry data and send it to the AO Supervisory Control system or the RTC Disk Sub-System as required.

- 6. The RTC interacts with the telescope system and the AO Control through two Ethernet connections: one connected to the RTC Control Processor (CP) and one connected to the RTC Disk Sub-system.

Additionally the functionality provided will be used to compensate for vibrations in the telescope system.

# 1.5 Algorithm

The mathematical derivation of each component algorithm of the RTC is described in "Gavel, D., NGAO Real Time Control Algorithms Document, KAON xxx, 2009". The component algorithms consist of:

- Wavefront sensor image processing

- Hartmann sensor wavefront reconstruction convert slopes to phases

- Inverse Tomography

- Conversion of desired phases to DM and TTM drive voltages

- Offloading

Details are given in KAON xxx, but we will briefly go over two key algorithmic steps, wavefront sensing and inverse tomography, here and describe how they map to basic elemental operations in the RTC.

# 1.5.1 Wavefront Reconstruction Algorithm

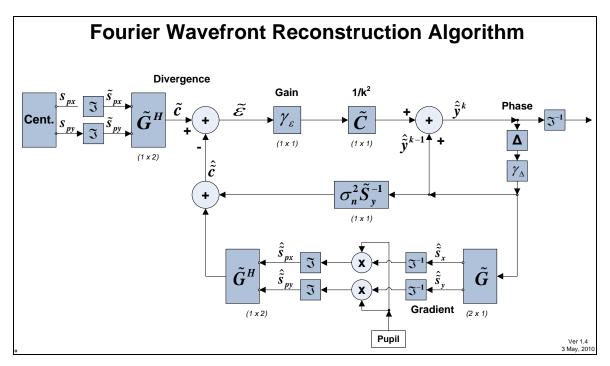

Figure 2 Wave Front Reconstruction Algorithm for HOWFS and NGS

The purpose of the wavefront reconstructor is to convert Hartmann slope data given on the aperture to an estimate of the wavefront phase. The following series of steps are performed for each wavefront sensor in the system:

- The wavefront slope data are compared to the gradient of the current estimate of the wavefront.

- The residual is converted to the Fourier domain where the approximate inverse to the gradient operator is applied.

- For the next iteration of the loop, it is important to compare slopes only within the aperture, where valid measurements exist. This is done by converting back to the spatial domain and selecting, via a pupil mask, the estimate gradients from within the aperture.

- The resulting estimate of wavefront phase is available for the next stage of the process, inverse tomography.

# 1.5.2 **Inverse Tomography**

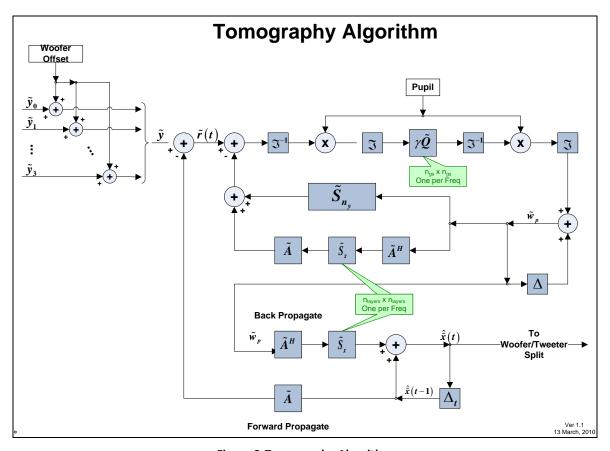

Figure 3 Tomography Algorithm

Inverse tomography consists of this sequence of operations:

- Gather the reconstructed wavefronts from each high-order wavefront sensor (these are already in the Fourier domain)

- Compare the wavefront phases to the prior estimate of what the wavefront phases would be if determined from the modeled atmospheric volume

- With this residual, perform an iteration that determines the preconditioned wavefront phase (see Algorithm Design Document, section 2.2). This step involves converting into and out of the spatial domain and applying the aperture data selection mask (labeled "Pupil" in the diagram).

- Back-propagate the preconditioned wavefront phase residuals and co-add to the volume delta-index estimates.

- The next step is to determine what wavefront is to be placed on the science deformable mirror, given the volume delta-index estimates. This is done by a forward propagating the volume delta-index estimates to the ground, summing all the layers in a mimic of ray tracing.

All the algorithms that need to be performed in real time, including the key functions described above, can be broken down into a set of basic elemental operations that must be performed by the RTC high-speed processor. The elemental operational elements are:

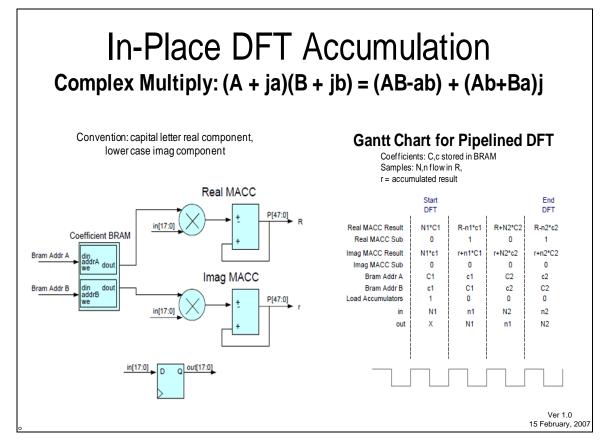

- 2-D Fourier Transform

- Element-wise multiply-accumulate (includes spectral domain filtering)

- Interpolation along transverse directions in the layer plane

- Matrix multiplication of small arrays: #guidestars X #guidestars

- Propagation ray-tracing between layers

- Non-linearity compensation by lookup tables

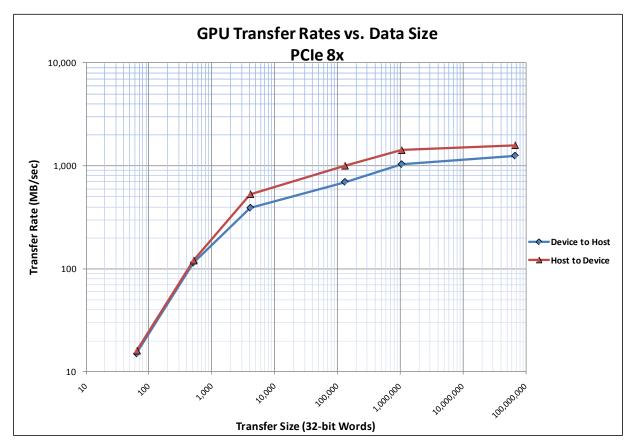

We have explored the implementation of each of these elemental steps in both FPGA and GPU processor architectures. Comparison results for the Fourier-transform pair, the single most time-consuming computation, is shown in and Appendix B.

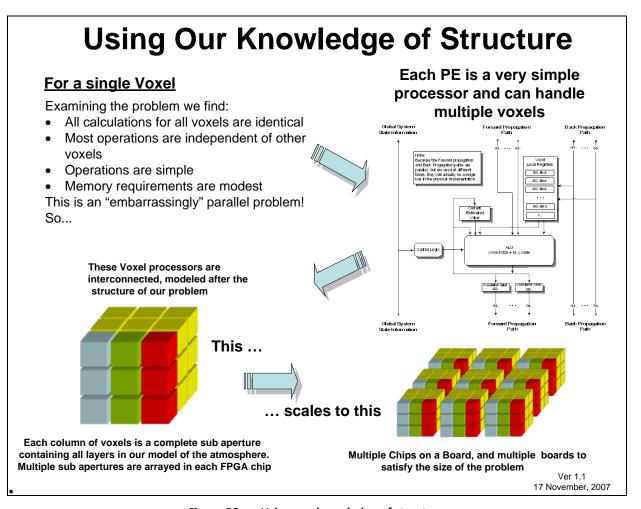

### 1.5.3 Massive Parallelization

Each of the elemental operations involves processing moderate amounts of data but they need to be done at extremely high speed. Much of the operation on these datasets can proceed in parallel, achieving a speed-up benefit that becomes essential to meeting the bandwidth and latency requirements of NGAO. By assigning small compute elements assigned to each spatial domain sample, or to each spatial frequency sample, all of the elemental operations, with the exception of the Fourier Transform, are on the order of N times faster than they would be in a corresponding conventional single CPU implementation, where N is the number of sample points (N~4000 for NGAO).

The Fourier transform is sped up by factor on the order log(N), using the algorithm described in Appendix G.

### 1.6 Functional Architecture

The NGAO RTC is not a single computer or controller. It consists of many different computers and processors (about 10) each performing different functions simultaneously, but with their inputs and outputs synchronized to perform the overall task of correcting the science wave front.

Figure 1 is a top level view of the overall system and its relationship to the AO Control. Figure 4 depicts the overall design, emphasizing real-time signal flow.

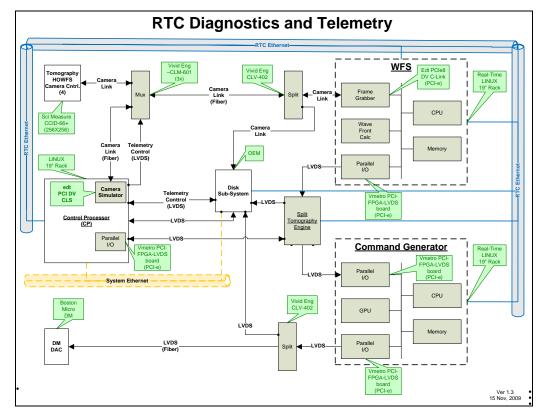

Figure 47 highlights the flow of telemetry, diagnostic, and offload-data.

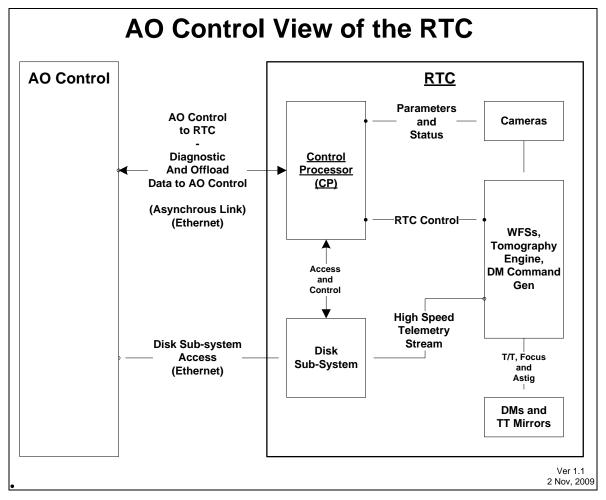

Figure 4 Top-level view of the AO Control's View of the RTC. See Figure 8 for a detailed view.

The RTC System is a real-time digital control system that operates on a fixed clock cycle, referred to as the Frame Clock. Each frame, the RTC takes data from various cameras, processes it, and updates the various mirrors and DMs for which it is responsible.

It runs the same program on each frame, with different data, but the same parameters, repeatedly, until the AO Control causes it to change.

The Control Processor (CP) acts as the synchronizing interface between the AO Control and the rest of the RTC, which is frame-clock driven. The AO Control processor will be implemented with a multi-processor computer running the Linux operating system with a real-time kernel. Synchronization with the frame-clock driven portion of the RTC is described in Sections 4 and 12.

The parameter loading determines the "state" of the RTC. This loading occurs in the background to the real-time cycles. Parameter updates occur synchronized to the frame clock. This insures that all information processed during a frame is processed with the same parameters.

# 1.6.1 Control Processor (CP)

The RTC Control Processor (CP) provides an asynchronous interface between the RTC system the AO Control. The interface to the AO Control is through a socket interface over Ethernet (See Figure 4 and Figure 18).

It is built on a high performance Linux server with a real-time kernel.

The RTC system is a key component to the overall NGAO system and the rest of the telescope environment. The CP's interface with the AO Supervisory Control and the telescope system will adhere to the component architecture defined in **FR-1418**.

# 1.6.2 Wave Front Sensors (WFS)

A short overview: There are two types of WFS in the NGAO RTC: low order (LOWFS) and high order (HOWFS).

### 1.6.2.1 LOWFS

There are 3 LOWFS, which use a IR natural guide stars (NGS) to estimate tip/tilt. One, the TTFA, also captures data for focus and astigmatism analysis.

A low-order wavefront sensor (LOWFS) processor is responsible for converting raw camera pixel data into a tip/tilt signal, plus focus and astigmatism numbers for the one TTFA sensor. For algorithm details, see Gavel, D., NGAO Real Time Control Algorithms Document, KAON xxx, 2009. Each LOWFS camera operates in parallel and feeds its data to the LOWFS. The LOWFS processes the data and sends commands to the science tip/tilt actuator on the Woofer and to the tomography engine.

### 1.6.2.2 HOWFS

There are two types of HOWFS: the Point-and-Shoot HOWFS are used to sharpen the NGS tip/tilt stars and are 32x32 sub-apertures in size; the Tomography HOWFS provide information to perform tomography in the science field of view and are 64x64 sub-apertures in size.

In the NGS mode, one of the Tomography HOWFSs serves as the WFS for the NGS and operates using 32x32 subapertures instead of 64x64. In this mode the other Tomography HOWFSs are not used. The output of the NGS/Tomography HOWFS is passed through the tomography engine unmodified and directly to the science object DM command generator.

Figure 5 Point-and-Shoot HOWFS/LOWFS Pair

A high-order wavefront sensor processor is responsible for converting raw Hartmann WFS camera pixel data into an array of wavefront phase measurements spaced on a regular grid in a coordinate system that defined as common throughout the AO system. HOWFS use a laser guide star (LGS) to probe the atmosphere and determine the high order atmospheric distortion in that direction.

The Point-and-shoot HOWFS first generates a wave front to correct light in the direction of the LGS. This wave front is then converted to DM commands that are used to determine the shape of a DM. This DM is used to sharpen their associated LOWFS NGS.

The tomography HOWFSs provide probing of the atmospheric volume containing the science object and generate a wave front in the direction of the LGS. These wave fronts are processed by the tomography engine and used to estimate the volume in the direction of the science object. The estimate of the volume is in turn used to provide a wave front to correct light in that direction. This wave front is passed to a DM command generator to place the desired shape on the science DM.

Each tomography HOWFS wavefront sensor has an associated wavefront sensor processor. These operate in parallel then feed their aggregate results to the tomography engine.

The architecture for the hardware for all WFSs follows the massively parallel approach. First, each wavefront sensor has an associated wave front sensor processor card, operating in parallel with but otherwise independent of (other than the frame synchronization clock) every other processor card.

The baseline design for a WFS processors card uses FPGAs. We have investigated the use of GPUs as an option, and they look to be a promising alternative, however for the remainder of this document, and the description of the baseline architecture and processing, we assume these are FPGA based cards.

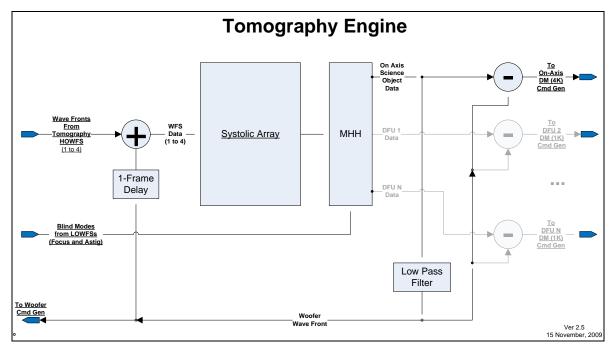

# 1.6.3 **Tomography Engine**

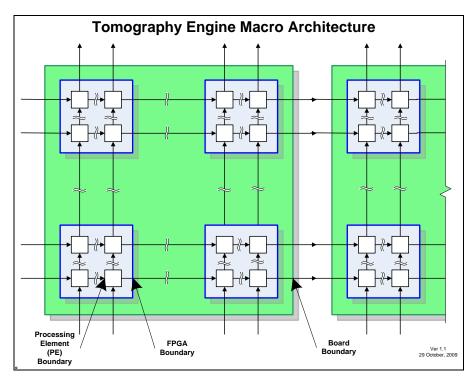

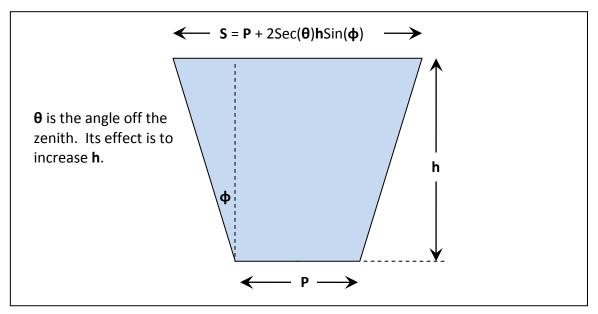

The tomography engine's Processing Elements are mapped "horizontally" over the aperture, and "vertically" over the layers of the model atmosphere. A given processing element (PE) on this map is assigned a piece of the aperture and alternates processing a portion of either the spatial or Fourier domain of it.

Figure 6 Processing Elements Mapping to the Atmospheric Model

Figure 7 Mapping Processing Elements to the Problem

All computational elements run the identical program, albeit with different parameters and data. Each processor in the tomography engine is connected to its four neighboring elements (representing the next spatial frequency over in both directions) because is it necessary to shift data to neighbors in order to implement the Fourier transform and interpolation steps in the tomography algorithm.

### 1.6.4 **DM Command Generators**

The Point-and-Shoot HOWFS's output and the tomography engine's output wavefronts are sent to the deformable mirror command generators for their DMs. These are dedicated units, one per DM. They take desired wavefronts in and produce DM command voltages that result in the correct wavefront, taking into account actuator influence functions and nonlinearities of each DM, see Figure 1.

## 1.6.5 **Disk Sub-System**

The RTC Disk Sub-System (see Figure 4) is an extremely high performance, large storage system that is designed to capture system Telemetry data that can be generated by the RTC. This data can be generated at over 2 GBytes/sec. This system is designed to be able to capture this data for an extended period, but it is not intended to be an archival system for long-term storage or access. The system has a capacity to store up to 60 terra bytes of data, which could be filled in a matter of days of heavy use.

Likewise, no data base facilities are provided beyond normal directory services.

# 1.6.6 Global RTC System Timing

Accurate time stamping of data will be provided (to 0.1 msec) for the telemetry stream. This will provide timing information for the various telemetry and other data products produced by the RTC. It is important that any science data be synchronized to this time stamp, see Appendix C.

# 1.6.7 Diagnostics and Telemetry Stream

All major data signals can be sent to the Telemetry/Diagnostic stream at the request of the AO Control. Any data in this stream can be sent to either-or-both the AO Control, for diagnostics, or the RTC disk sub-system, for storage. (See: Section 9)

Data that can be saved through Telemetry or viewed through Diagnostics include (See Section 9):

- Raw Camera Data for HOWFS and LOWFS

- 2. HOWFS Centroids

- 3. HOWFS Wave Fronts

- 4. Tip/Tilt for all WFS + Focus and Astigmatism for the TTFA LOWFS

- 5. Science on-axis T/T

- 6. Tomographic Layers

- 7. Science on-axis unfiltered Wave Front

- 8. Science on-axis High Order Wave Front

- 9. Science on-axis Woofer Wave Front

- 10. Science on-axis High Order Commands

- 11. Science on-axis Woofer Commands

- 12. RTC Current Parameter Settings

All Diagnostic information is time stamped accurate to one Frame Time.

## 1.7 Physical Architecture

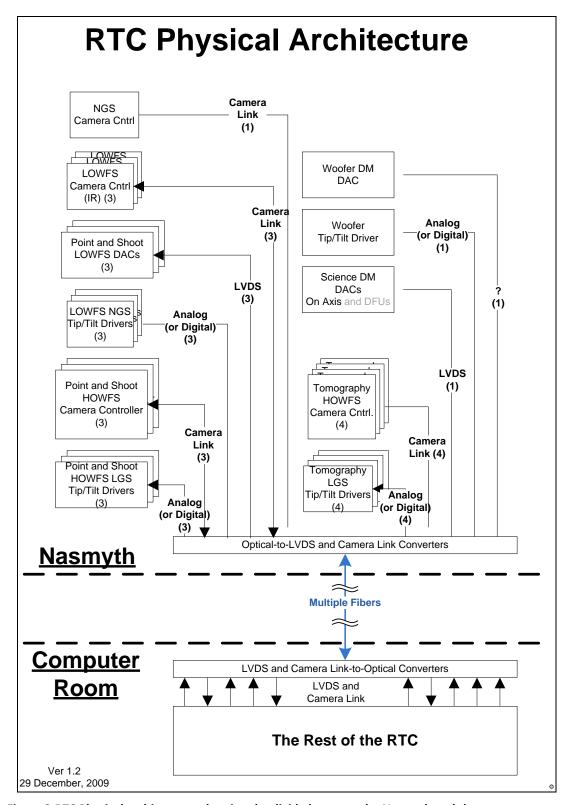

The RTC consists of over 15 computers, require several cubic meters of space, and dissipate over 5KW. To minimize the heat and space requirements on the Nasmyth platform, only the equipment which requires proximity to the AO optics are placed on the Nasmyth. The rest are housed in the computer room below the telescope.

Figure 8 shows the RTC and all sub-systems. The RTC is physically divided between the Nasmyth and the computer room below the telescope. The cameras, their controllers, the DMs, and their controllers are located on the Nasmyth, see Figure 9. The rest of the RTC, the WFS, tomography engine, disk sub-system, DM command generators, control processor, and

clock generator are located in the computer room. The two sections are connected by high-speed fiber links.

Figure 8 Overview of the RTC sub-systems

Note: Since this is an overview, not all interfaces and data paths are shown.

Figure 9 RTC Physical architecture, showing the divide between the Nasmyth and the computer room

### **Include NGS**

# 1.8 Implementation Alternatives

As part of the design process, we have investigated a number of alternative architectures and hardware implementation alternatives. For the sake of the design, we are recommending that FPGA boards be used for wavefront sensing and tomography in the frame-clock driven portion of the RTC. The decision for this baseline is based on one of conservativeness: the approach is well characterized and has been demonstrated in low-level simulators, the timing requirements are clearly met, and the process of specifying and building these boards is a clearly established technology within the industry. The drawbacks are the additional cost of custom board design and sparing, so for this reason we have investigated the use of commercial off-the-shelf alternatives: multi-core CPUs and GPUs. We describe our findings below.

### 1.8.1 Multi-core CPUs

Multi-core CPUs are the traditional method of implementation. The support parallelization and have very high clock rates. However, maximum parallelization is limited to the number of cores per CPU and the number of CPUs.

### 1.8.2 **FPGAs**

FPGAs are containers of a very large amount of unconfigured logic (millions of logic gates) that can be personalized to the needs of the users. This gives extreme flexibility to design logic that is not available as a commercial off the shelf product.

In our application of FPGAs to the tomography engine, we are able to create many 100's of simple interconnected processors per chip to execute the tomography algorithm.

### 1.8.3 **GPUs**

GPUs are extremely efficient at operations that can be parallized and stay within the GPU itself. Since they are co-processors processors to the CPUs in a system, care must be taken to synchronize the two and minimize transfer times, see Appendix B.

### 1.8.4 Recommended implementations

We have examined different candidate technology implementations for the key stages of the RTC. Here are our findings

- Each WFS reconstructor can be implemented using one conventional multi-core multi-CPU solution (for example the GPI processor, which is uses 4 quad-core Xeon processors, one per WFS), or one custom FPGA card, or one advanced-technology GPU card (potentially). The GPU driver would need a custom driver to allow direct memory access for loading of camera data, something that present GPUs don't offer. Although we are continuing to hold the alternatives as potential cost-savers, the baseline WFS reconstructor is implemented on an FPGA based card.

- The Tomography Engine can only meet requirements if it is implanted with a multiple card system based on FPGAs. The NGAO requirements are met with a 9-FPGA systolic array arrangement, based on the XILINX Vertex-6 chip as a baseline.

• The DM Command Generation can be implemented using logic wrapped around a static memory on a custom board, or on a GPU. FPGA implementation is rejected because the two-entry nonlinear lookup table needed for open-loop MEMS DM control requires a large amount of memory on each computing element, more than current FPGAs provide. We have therefore established commercial GPUs, one per deformable mirror as the baseline DM command generator. GPUs provide both the necessary speed and memory. Communications are the bottleneck, but the necessary data rates are achieved via the PCI-bus interface available on current commercial GPU cards. Both the input, from the tomography engine, and the output, to the DM driver, are via the PCI-bus interface.

# 2. System Characteristics

This section provides the basic RTC system characteristics and assumptions for the operating conditions it is designed to operate in. The assumptions are taken either from the Functional Performance Requirements (FPR) database, or from the error budget spreadsheets (with the FPRs taking precedence).

# 2.1 Assumptions and Performance Requirements

| Item<br>No. | Assumptions                                         | Value | Units   |

|-------------|-----------------------------------------------------|-------|---------|

| 1           | Wind                                                | 9.5   | m/sec   |

| 2           | Sub Aperture Size                                   | 16.6  | cm      |

| 3           | Max Zenith Angle                                    | 54    | degrees |

| 4           | Frame Rate                                          | 2     | KHz     |

| 5           | Stare Time HOWFS                                    | 500   | μsec    |

| 6           | Stare Time LOWFS                                    | 500   | μsec    |

| 7           | Sub Apertures Across Primary                        | 60    |         |

| 8           | Sub Apertures Used in Calculations                  | 88    |         |

| 9           | Number of Tomography Layers                         | 5     |         |

| 10          | Number of Tomography WFSs                           | 4     |         |

| 11          | Number of WFSs for Tip/Tilt, focus, and astigmatism | 3     |         |

| 12          | Number of Science Objects                           | 1     |         |

Table 1 NGAO RTC System Assumptions

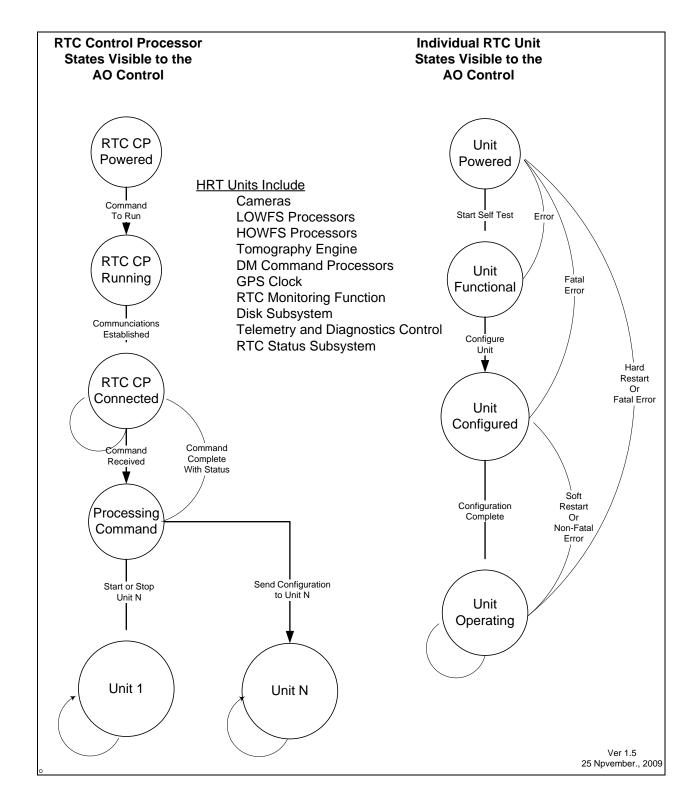

# 2.1 RTC States Visible to the AO Control

There are multiple levels of states in the AO control system including the supervisory control. This section describes only those states that the RTC itself needs to keep track of. These states are limited and insure only that the RTC cannot damage itself, will not give invalid data, and that it can be controlled to move between states become functional or be shut down.

Figure 10 shows the states visible to the AO control.

Finer grained information may be available for diagnostics, but are not presented here.

Figure 10 RTC and Sub-System States Viewable by the AO Control

The RTC CP will not honor a request to do something that is not valid, given its current state, and will return an appropriate error to the AO Control.

### Examples:

- 1. If a sub-system has not been configured and the AO Control attempts to start the sub-system, the RTC will return an error indicating "Not Configured".

- 2. If the AO Control attempts to set a parameter with a value that is out of the allowable bounds for that parameter, the RTC will return and error indicating "Out of Bounds" with an additional message that indicates the allowable bounds. This is not really a "state" issue, but is mentioned here for clarity.

- 3. However, if the AO Control attempts to set a parameter with a valid value but one that does not make sense in the presence of other parameters that have been set, the RTC will simply set that parameter. The states represented by various combinations of settable parameters have meaning to a higher level of control than the RTC and should be controlled at that level.

# 2.2 Timing and Control of Internal States of the RTC

See Section 2.1 for a discussion of the States of the RTC visible to the AO Control.

Several sub-systems of the RTC run at different rates or start at different times during operation. Both the LOWFSs and the HOWFSs can run at approximately 2 KHz. The basic frame rate of the RTC is determined by the current rate of the camera with the fastest frame rate. All cameras and Tip/Tilt data must be synchronized to an integer multiple of this rate

Commands to change parameters come from the AO Control asynchronously. The RTC synchronizes these changes in parameters or data to occur at the start of the above frame rate, ~2 KHz. This ensures that all processing that occurs during a frame is done with the same parameters and input data.

Anything arriving too late to be applied at the start of a frame will be applied at the start of the next frame.

# 2.3 Reliability and Recoverability

The RTC will have a failure rate of less than 1 per 200 hours of operation. It constantly monitors itself for errors and will notify the AO Control with appropriate messages, logs, and alarms as determined by the AO Control. The primary cause of errors will be Single Event Upsets due to cosmic rays and related events. We constantly monitor for these events and can recover from them in less than 5 minutes. This can be either automatically or under control of an operator. A hardware signal is available to close the science shutter when an error is discovered and can be opened when the problem is resolved, either manually or automatically as preferred.

### 2.3.1 **SEUs**

An SEU is a single event upset in the system, usually caused by neutron showers from cosmic rays in the atmosphere. Alpha particles from concrete or other materials can also cause them.

When these particles strike electronic circuitry, the result can be to switch the state of some elements, such as memory.

SEU events normally leave no lasting damage to the circuitry, so that once detected, we can remedy their effect by reloading the memory with the correct value.

# 3. Error Budgets, Latency, and Data Rates

Table 2 shows the major latency components for the RTC.

| RTC Latency Summary       | (µSec) | Notes |

|---------------------------|--------|-------|

| Camera Stare              | 250    | 1     |

| CCD Read                  | 500    | 2     |

| WFS                       | 300    | 3     |

| Tomography                | 450    | 4     |

| Command Generation        | 200    | 5     |

| DM Hold                   | 250    | 6     |

| Latency Contingency (~5%) | 100    |       |

| Total Latency             | 2050   |       |

Table 2 NGAO RTC Latency Summary

### Scrub this for consistency and add derivation for clarity.

### Notes:

- 1. This is one half the time for a single camera to capture an image from the LGS. It is a function of the CCD and camera controller settings.

- 2. This is the time to read the CCD. It can be partially overlapped with the WFS calculations and this is already included in the timing.

- 3. This is the time that includes reading the CCD, Centroiding, reconstructing the wave front, and transferring it to the Tomography Engine. Reading the CCD, grabbing the frame, and computing the centroids may be overlapped in some implementations.

- These values are based on analysis and measurements done for the GPI AOC [4]. This is a similar sized problem.

- 4. This is the time to combine the wave fronts from the tomography HOWFS, compute the estimate of the atmosphere, forward propagate the science object, and transfer the data to the low and high order command generators for the science object DMs.

- This is based on simulations and calculations summarized in Appendix D.

- 5. This is the time to generate the commands for the science object DMs and transfer them.

- 6. This is one half the time the commands are held on the DM. It is the same as the camera stare time.

# 3.1 Error Budgets

The error budgets in this document come from the NGAO Requirements Database. These numbers are expressed in nanometers or milliarcseconds.

They can be the result measurement noise or resolution, computational accuracy, algorithms, A/D accuracy, accuracy of our DM model, or other factors or of latency, which is the primary source or error in the RTC control system.

# 3.1.1 Accuracy

The accuracy of a system is determined by several factors. In our system, they are the accuracy of the:

- Camera data

- Parameters used in calculations

- Algorithms used

- Arithmetic operations

- Output hardware

### 3.1.1.1 Camera Data

The camera data supplied is 16 bits. We have assumed that the camera data is accurate to 12 bits.

### 3.1.1.2 Parameters

All fixed parameters and arrays used in calculations are represented as 18-bit numbers for real values with an added 18-bit imaginary part if they are complex. Examples of the parameters are  ${\rm C_n}^2$ , Fourier coefficients, Kolmogorov filter coefficients, asterism parameters, DM modeling tables, etc.

## 3.1.1.3 Algorithms

Both the wavefront reconstruction and tomography steps require iteration. Upon convergence, the wavefronts at the output of the wavefront reconstruction and the output of the tomography engine, have achieved the match to data to the accuracy of the machine word length. The word length is selected so that digitization error is less than other physical limits, such as wavefront measurement error due to photon noise. The current error budget has this set at a few nanometers, and given that starting wavefronts are several microns RMS, the 18 bit word length baseline for use in the RTC was deemed sufficient.

The Hartmann centroiding error depends on the photon-counting and read-noise properties of the wavefront sensor. The digitization error, or photon noise, whichever is dominant, carries over to the error in the reconstructed wavefront. The 12-bit camera pixel data is sufficient to process the 1000 detected photo-electrons per Hartmann spot per frame to a level well below its inherent 33:1 signal to noise ratio set by photon noise.

The tomography algorithm is designed to converge to a minimum variance solution. Again, the digitization word length is chosen to represent numbers well below the expected residual

tomography wavefront error. The residual error is expected to be in the 10 nm regime, and since the whole wavefront is on the order of 10's of microns rms, a signal to noise of at least 1000:1 (10 bits) needs to be maintained in all calculations, in particular the subtraction in the iteration loop. 18 bit calculations are the baseline.

DM command generation requires the use of a non-linear functional lookup. Because nonlinearities change the bit accuracy between input to the table and output, the D/A converter word length is designed to maintain the resulting wavefront control accuracy to below the assigned error budget number. At the fasted part of the MEMS nonlinear response curve, the wavefront is changing at about 100 nm/V, so ~100 mm out of a total of 240 V accuracy is needed on the D/A, or about 12 bits.

The nonlinear model for open loop DM control is accurate to about 30 nm wavefront (15 nm surface), so a signal to noise on the order of 1000:1 should be maintained during the process of non-linear function fit. The baseline design is to use the GPU to implement 100-coefficient spline functions to map mirror displacements and forces to MEMS drive voltages. Accuracy of this technique well exceeds the 30 nm inherent accuracy of the model. The model is established with a calibration process performed on the MEMS DM. The calibration visits 400 force and displacement points in a 20x20 array [reference Morzinski paper], recording the voltages at each of these points. The resulting voltage surface is quite smooth and is accurately modeled by the 100-coefficient spline method. The GPU must now complete this operation for all the actuators on the DM within the margin of the latency time allocated to it.

# 3.1.1.4 Arithmetic Operations

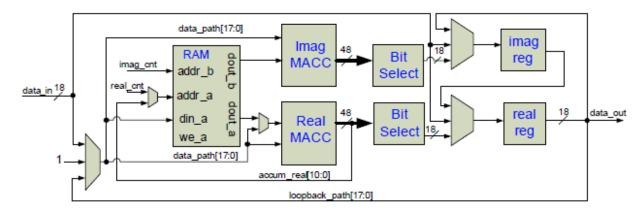

Individual arithmetic operations take 18-bit values and accumulate a 48-bit result.

### 3.1.1.5 DACs

The DM's are supplied with 14-bit values.

# 3.2 Latency Summary

The most significant element to overcome in an AO system is the latency between sampling the atmospheric turbulence and applying the compensation for it. See Sect 4.1.1 of the Algorithm document for calculations on the impact of latency components on the wavefront error.

It and the spatial sampling determine the rate at which calculations and data transfers must be made to achieve a given level of compensation.

These in turn determine the size of the computation engine that is needed to handle the problem. For the current NGAO specification, this is a terra operation per second problem, which directly affects and limits the choices of algorithms, architectures, and implementations.

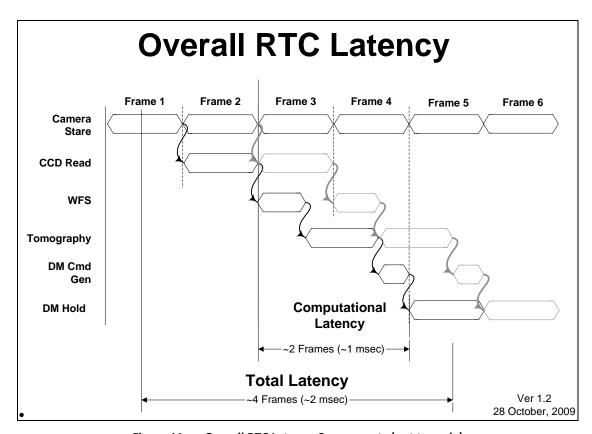

The total RTC latency is made up of several components, illustrated in Figure 11. The time to transfer data between processing units is included in the times for that unit.

Camera Stare is the time the CCD is collecting light for a given frame.

Only half the time of camera stare is counted as latency because the value measured at the end of the stare time is the integrated value over the entire time.

- CCD Read is the time to read the CCD while it is collecting the light for the next frame

- WFS is the time to perform centroiding and reconstruction of the wavefront

- Tomography is the time to take the 4 tomography wavefronts, update the estimate of the atmosphere and forward propagate the correct wavefront correction in the science direction.

- DM Command generation is the time to take the science wavefront and determine the correct voltages to place on the DM to achieve the desired shape.

- DM Hold time is the amount of time the shape remains on the DM and is the same as the Camera Stare time.

Only half the time of the DM hold is counted as latency because the effect of the shape applied is integrated over the time it is on the mirror.

Figure 11 Overall RTC Latency Components (not to scale)

The total latency is calculated from the midpoint of the camera stare time to the midpoint of the subsequent DM hold-time. Computational Latency includes only the portion of time due to our actual processing of the data.

# 3.2.1 Architectural Issues Affecting Latency

Processing system architectures can be divided into two major categories: non-pipelined and pipelined. The following discussions attempts to highlight the differences between the two. One is not better than the other except in the context of the requirements and limitations of the system to which they are applied.

In the two examples that follow, it is assumed that the total processing time is the same in each case. The effects on the minimum total latency is examined. The example timings are for 900  $\mu$ sec msec of computational latency, 400  $\mu$ sec for the longest element of the computational latency, and 500  $\mu$ sec to read the CCD. The time to perform centroiding can be overlapped with the CCD read and are ignored. However, the reconstruction and tomography cannot effectively start until all the centroids have been processed.

# 3.2.1.1 The effect of wind prediction and compensation on latency errors

Computations and operations to calculate the DM commands to place on the mirrors to reduce the effect of the atmospheric turbulence add to our latency. However, there is only so much we can do to reduce them. The estimate we create of the turbulence on each layer is old by the time it is placed on the DM and the layers have now moved.

However, at the frame rates at which we operate, the turbulence is primarily frozen flow with various layers of "fixed" turbulence blown across our aperture. If we know the speed of the wind in each layer, we can easily shift our estimate to be consistent with the how much the layer has moved since we measured it.

Measuring and compensating for the wind in the layers can dramatically reduce the effective latency of the RTC and hence the errors attributed to it.

The RTC has the capability to compensate for the wind layer by layer at virtually no added cost in latency or hardware. Wind induced shift – given the wind velocity at each layer in the tomography – is implanted with a simple shift factor, a multiplication in the Fourier domain. However, the wind velocity estimation portion of the problem needs to be a separate calculation.

Fortunately, wind estimation can be done off-line, in parallel with the RTC calculations. A method advance by Johnson [reference Luke Johnson's OSA 2009 paper] utilizes the telemetry data from the AO system to optimally estimate the wind velocity, assuming this velocity vector is changing slowly relative to the time scale of the frame rate.

Latency error could potentially be reduced significantly using the information, since pre-shifting the prior wavefront estimate by the estimated frozen-flow amount is tantamount to increasing  $\tau_0$ . This is true even though the wind velocity estimates lag the RTC measurements, from which they were generated, by many frames. As long as the wind is not changing faster than the lag, it can benefit.

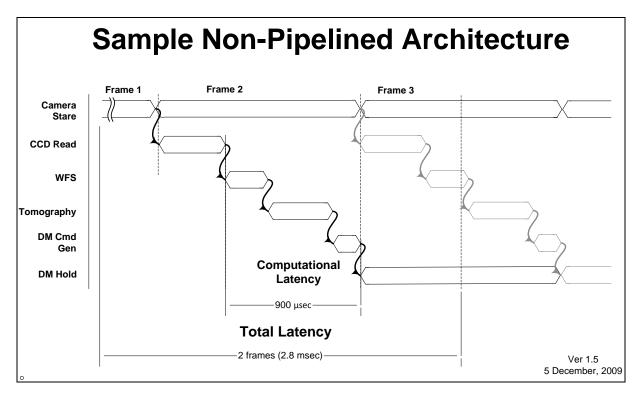

# 3.2.1.2 Non-Pipelined Architectures

The following describes an example of a non-pipelined MOAO control system. It does not represent the current RTC timing and is provided for illustration only.

In a non-pipelined system, data is brought in, processed by a single processing unit, the results are used, and the cycle is started again. In our case, we have a computational latency of 1 msec and a CCD read time of 500  $\mu$ sec. Since there the processing unit is busy processing the last frame, no processing can occur during the next CCD read. The resultant frame rate is 1.5 msec and the total latency is 3 msec.

Figure 12 Non-Pipelined Latency (not to scale)

In a non-pipelined system, the frame rate is determined by the total latency of handling the data. In this case, it is the time to read the CCD plus the computational latency.

All calculations must be finished before new calculations can start. The total latency is two frames (1 frame to handle the data, plus  $\frac{1}{2}$  a frame on the front end to account for the integration time of the camera and  $\frac{1}{2}$  a frame at the end to account for the integrated effect of the DM hold time).

### 3.2.1.3 Pipelined Architectures

The following describes an example of a pipelined MOAO control system. It does not represent the current RTC timing and is provided for illustration only.

In a pipelined system, the processing is divided amongst several units. Each unit processes the data and passes it on to the next unit. The total computational Latency is still 1 msec, as above (assuming transfer times between units are negligible). However, it can be seen that new data can be brought in as soon as the first unit is through processing its last data, and the output can

be updated as soon as the last unit has processed its data. The frame rate here is determined by the largest time spent by any individual unit. Consequently, this rate can be considerably faster than that in the non-pipelined case.

Note that the camera frame rate is the same as the DM frame rate. The DM rate is synchronous but has a different phase than the camera's.

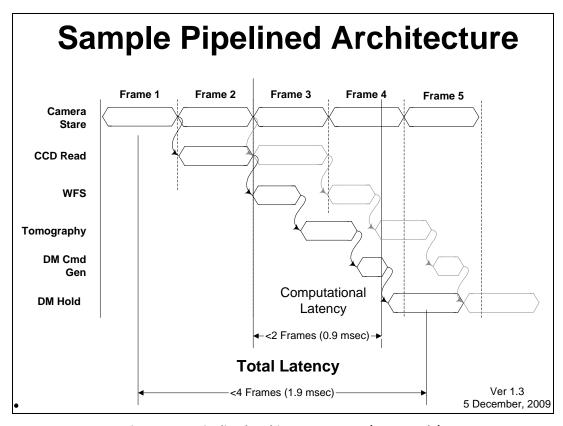

Figure 13 Pipelined Architecture Latency (not to scale)

In this system, each element of the data processing is handled by separate hardware. This allows us to have several frames of camera data being processed somewhere in the pipe at the same time, just not in the same piece of hardware. The maximum frame rate is determined by the longest time it takes for any single element to process its data.

In our situation, the frame rate is determined by the CCD read time, which happens to be 500  $\mu$ sec. All other individual computational elements are less than this. The time to handle the data is the time to read the CCD plus the Computational Latency , <3 Frames (1.4 msec). The total latency is 1.9  $\mu$ sec, <4 frames (3 frames to handle the data, plus ½ a frame on the front end to account for the integration time of the camera and ½ a frame at the end to account for the integrated effect of the DM hold time).

Figure 13 shows that the computational Latency does not end on a frame boundary. While the DM commands are applied synchronous to the frame clock they are applied at a time that does not occur on a frame clock boundary.

Assuming the time to handle the data is the same for both the pipelined and the non-pipelined case, the pipelined architecture will provide less total latency. It can require more hardware, however.

# 3.2.1.4 Comparison of Non-Pipelined vs. Pipelined Architectures

A pipelined system takes more hardware and is more complex to implement than a non-pipelined system. However, the benefits are that we can decouple the frame rate from the processing time and achieve a lower latency time. In our case, the latency difference is 2.8 msec vs. 1.9 msec. a savings of 900 µsec or 30%.

For the NGAO RTC, we use a pipelined architecture.

# 3.2.2 Latency Calculations for NGAO

The times for executing the RTC algorithms were derived as follows:

- Detailed FPGA simulations to verify that the basic tomography loop functioned correctly and at the desired clock rate.

- Extending the algorithm for additional functionality and counting clocks needed to execute the code for these functions, see Appendix D.

- Timing tests and analysis for the Gemini Planet Imager AO Control were used for CPU operations [4].

- Timing tests and analysis for the GPU were used for CPU operations.

# 3.2.2.1 Latency Categories

Latency can be divided into three categories: transfer, compute, and fixed latencies.

Transfer latency is the result of moving data from one place to another, usually between physically distinct hardware.

Compute latency is due to the time it takes to apply an algorithm on the data, and includes any minor transfer latency that may occur during that process.

Fixed latency is due to system architecture issues that are separate from the above. In the case of the RTC, it is the result of the value of the frame clock and the time read the data out of the CCD subsequent from the actual time to transfer it to the WFS frame grabber.

Detailed latency analysis can be found in the sections below.